### (12) 特許協力条約に基づいて公開された国際出願

(19) 世界知的所有権機関 国際事務局

2020年1月2日(02.01.2020)

(43) 国際公開日

(10) 国際公開番号

# WO 2020/004021 A1

(51) 国際特許分類:

H01L 21/338 (2006.01) H01L 29/778 (2006.01) H01L 21/337 (2006.01) H01L 21/365 (2006.01) H01L 29/812 (2006.01)

(21) 国際出願番号: PCT/JP2019/023188

(22) 国際出願日: 2019年6月12日(12.06.2019)

(25) 国際出願の言語: 日本語

(26) 国際公開の言語: 日本語

(30) 優先権データ:

特願 2018-125452 2018年6月29日(29.06.2018) JP

(71) 出願人: パナソニック I Pマネジメント株式会 社(PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO., LTD.) [JP/JP]; 〒5406207 大阪府大阪市中央区城見2丁目1 番61号Osaka (JP).

- (72) 発明者: 野村 雅則(NOMURA, Masanori). 上野 弘明(UENO, Hiroaki). 木下 雄介(KINOSHITA, Yusuke). 山田 康博(YAMADA, Yasuhiro). 石田 秀俊(ISHIDA, Hidetoshi).

- (74) 代理人: 特 許 業 務 法 人 北 斗 特 許 事 務 所(HOKUTO PATENT ATTORNEYS OFFICE); 〒5300001 大阪府大阪市北区梅田一丁目 1 2 1 7梅田スクエアビル Osaka (JP).

- (81) 指定国(表示のない限り、全ての種類の国内保護が可能): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH,

(54) Title: BI-DIRECTIONAL SWITCH ELEMENT

(54) 発明の名称: 双方向スイッチ素子

(57) **Abstract:** The present invention addresses the problem of reducing current collapse. A bi-directional switch element (1) includes a substrate (2), an  $Al_zGa_{1-z}N$  layer (GaN layer 6), an  $Al_bGa_{1-b}N$  layer (first AlGaN layer 7), a first source electrode (S1), a first gate electrode (G1), a second gate electrode (G2), a second source electrode (S2), a p-type  $Al_{x1}Ga_{1-x1}N$  layer (first p-type AlGaN layer 81), a p-type  $Al_{x2}Ga_{1-x2}N$  layer (second p-type AlGaN layer 82), an  $Al_yGa_{1-y}N$  layer (second AlGaN layer 5), and an  $Al_wGa_{1-w}N$  layer (third AlGaN layer 4). The

CL, CN, CO, CR, CU, CZ, DE, DJ, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JO, JP, KE, KG, KH, KN, KP, KR, KW, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) 指定国(表示のない限り、全ての種類の広域保護が可能): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), ユーラシア (AM, AZ, BY, KG, KZ, RU, TJ, TM), ヨーロッパ (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

### 添付公開書類:

国際調査報告(条約第21条(3))

$Al_zGa_{1-z}N$  layer is formed on the substrate (2). The  $Al_bGa_{1-b}N$  layer is formed on the  $Al_zGa_{1-z}N$  layer. The  $Al_yGa_{1-y}N$  layer is interposed between the substrate (2) and the  $Al_zGa_{1-z}N$  layer. The  $Al_wGa_{1-w}N$  layer is interposed between the substrate (2) and the  $Al_yGa_{1-y}N$  layer, and has a concentration of C that is higher than that of the  $Al_yGa_{1-y}N$  layer.

(57) 要約:本開示の課題は、電流コラプスを抑制することである。双方向スイッチ素子(1)は、基板(2)、A I  $_z$  G a  $_{1-z}$  N層(G a N層 6)、A I  $_b$  G a  $_{1-b}$  N層(第1のA I G a N層 7)、第1のソース電極(S 1)、第1のゲート電極(G 1)、第2のゲート電極(G 2)、第2のソース電極(S 2)、p型 A I  $_{x\,1}$  G a  $_{1-x\,1}$  N層(第1の p型 A I G a N層 8 1)、p型 A I  $_{x\,2}$  G a  $_{1-x\,2}$  N層(第2の p型 A I G a N層 8 2)、A I  $_y$  G a  $_{1-y}$  N層(第2の A I G a N層 5)、及び A I  $_y$  G a  $_{1-w}$  N層(第3の A I G a N層 4)を備える。A I  $_z$  G a  $_{1-z}$  N層は、基板(2)上に形成されている。A I  $_y$  G a  $_{1-y}$  N層は、基板(2)と A I  $_z$  G a  $_{1-z}$  N層との間に介在している。A I  $_y$  G a  $_{1-y}$  N層との間に介在している。B I  $_y$  G a  $_{1-y}$  N層との間に介在し、A I  $_y$  G a  $_{1-y}$  N層との間に介在し、B I  $_y$  G a  $_{1-y}$  N層との間に介在し、A I  $_y$  G a  $_{1-y}$  N層との間に介在している。

# 明細書

発明の名称: 双方向スイッチ素子

# 技術分野

[0001] 本開示は、一般に双方向スイッチ素子に関し、より詳細には2つのゲート 電極を備える双方向スイッチ素子に関する。

# 背景技術

- [0002] 従来、ダブルゲート(デュアルゲート)の半導体素子である双方向スイッチ素子が提案されている(特許文献 1)。

- [0003] 特許文献1に記載された双方向スイッチ素子は、シリコンからなる導電性の基板上にAINからなるバッファ層を介在させて、半導体層積層体が形成されている。半導体層積層体は、アンドープのGaNからなる第1の層(GaN層)と、アンドープのAIGaNからなる第2の層(第1のAIGaN層)とが下側から順次積層されている。

- [0004] 第1の層の第2の層とのヘテロ界面近傍には、2次元電子ガス層であるチャネル領域が生成されている。

- [0005] 半導体層積層体の上には、互いに間隔をおいて第1のオーミック電極(第1のソース電極)及び第2のオーミック電極(第2のソース電極)が形成されている。半導体層積層体の上における第1のオーミック電極と第2のオーミック電極との間の領域に、第1のオーミック電極側から順に、第1のp型窒化物半導体層を介在させて形成された第1のゲート電極と、第2のp型窒化物半導体層を介在させて形成された第2のゲート電極と、が並んでいる。

- [0006] 特許文献1に記載の双方向スイッチ素子では、例えば基板を電気的にフローティングにした状態で使用された場合に、スイッチング時のオン抵抗が増加する電流コラプスが発生することがあった。電流コラプスは、高電圧印加時にチャネル近傍(結晶、界面等)に電子が捕獲され、オン抵抗が増大する現象である。

# 先行技術文献

# 特許文献

[0007] 特許文献1:特開2011-204993号公報

# 発明の概要

[0008] 本開示の目的は、電流コラプスを抑制することが可能な双方向スイッチ素子を提供することにある。

# 課題を解決するための手段

[0009] 本開示に係る一態様の双方向スイッチ素子は、基板と、AIzGa1-zN層 (ここで、 $0 \le z < 1$ ) と、 $A \mid_b G a_{1-b} N \mathbb{R}$  (ここで、0 < b < 1) と、 第1のソース電極と、第1のゲート電極と、第2のゲート電極と、第2のソ ース電極と、 p型 A I <sub>×1</sub> G a <sub>1-×1</sub> N層(ここで、 O ≦ x 1 ≦ 1 )と、 p型 A  $I_{\times 2}Ga_{1-\times 2}N$ 層(ここで、 $0 \le \times 2 \le 1$ )と、 $AI_{\times}Ga_{1-\times}N$ 層(ここで 、0 < y < 1、かつ、z < y < b)と、 $A \mid_{w} G a_{1-w} N$ 層(ここで、0 < w< 1、かつ、z < w < b)と、を備える。前記 $A \mid_z G a_{1-z} N$ 層は、前記基 板上に形成されている。前記AI。Ga1-bN層は、前記AI2Ga1-zN層上 に形成されている。前記第1のソース電極、前記1のゲート電極、前記第2 のゲート電極、及び、前記第2のソース電極は、前記AI<sub>b</sub>Ga<sub>1-b</sub>N層上に 形成されている。前記 p 型  $A \mid_{x_1} G \mid_{a_1-x_1} N$  層は、前記第 1 のゲート電極と 前記Al<sub>b</sub>Ga<sub>1-b</sub>N層との間に介在している。前記p型Al<sub>x2</sub>Ga<sub>1-x2</sub>N層 は、前記第2のゲート電極と前記A  $I_b$  G a  $I_{-b}$  N層との間に介在している。 前記AI、Ga1-、N層は、前記基板と前記AIZGa1-ZN層との間に介在し ている。前記AI、Ga1-、N層は、前記基板と前記AI、Ga1-、N層との間 に介在している。前記AI、Ga1-、N層のCの濃度は、前記AI、Ga1-、N 層のCの濃度よりも高い。

# 図面の簡単な説明

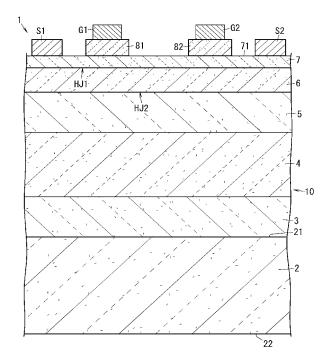

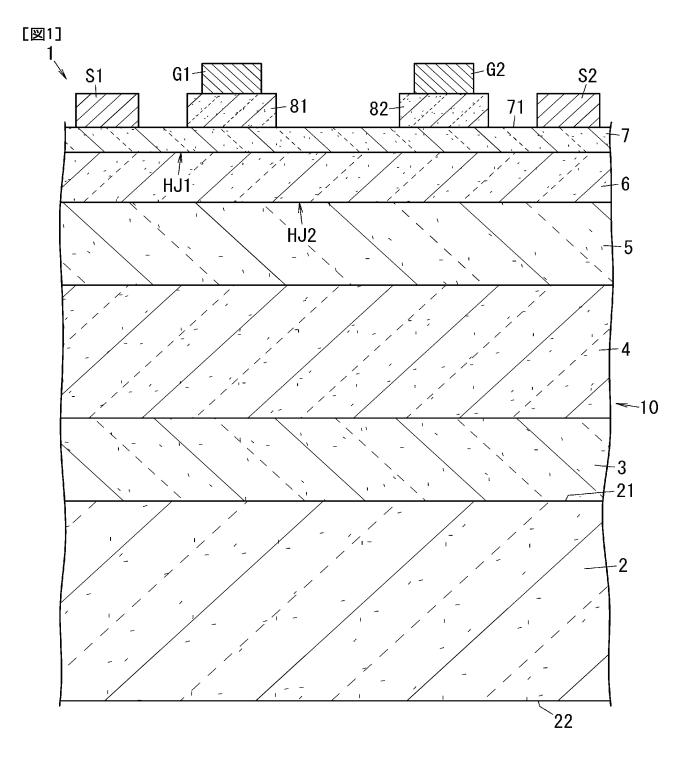

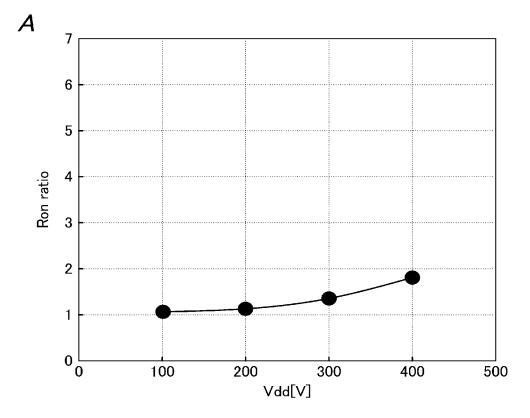

[0010] [図1]図1は、実施形態1に係る双方向スイッチ素子の断面図である。 [図2]図2Aは、実施形態1に係る双方向スイッチ素子のオン抵抗比-電圧特性図である。図2Bは、比較例に係る双方向スイッチ素子のオン抵抗比-電 圧特性図である。

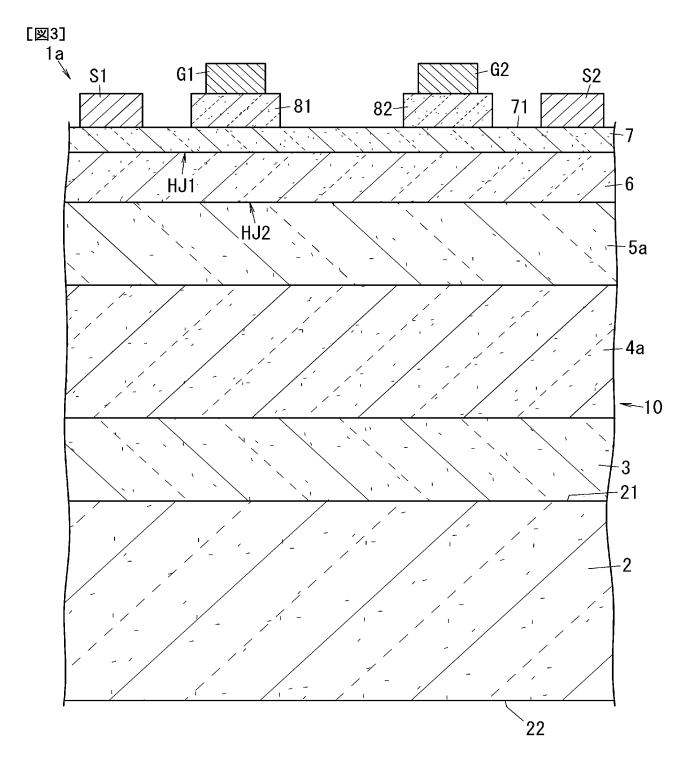

[図3]図3は、実施形態1の変形例に係る双方向スイッチ素子の断面図である。

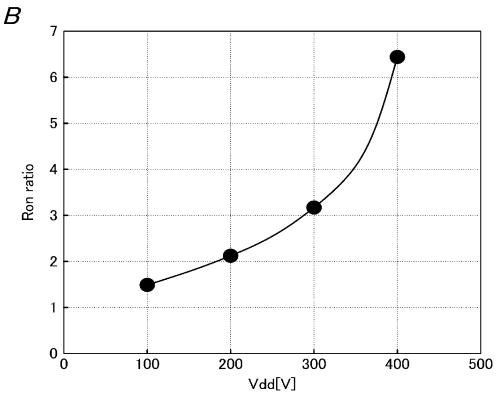

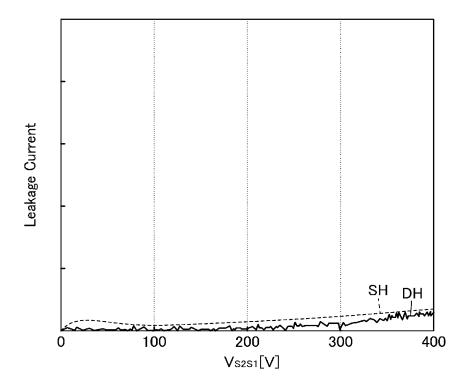

[図4]図4は、実施形態1に係る双方向スイッチ素子及び比較例に係る双方向スイッチ素子の電流-電圧特性図である。

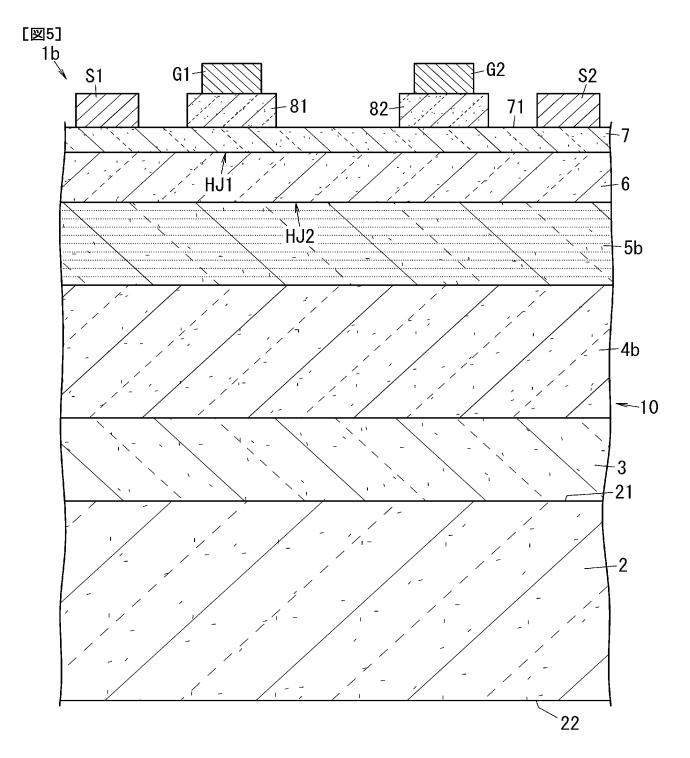

[図5]図5は、実施形態2に係る双方向スイッチ素子の断面図である。

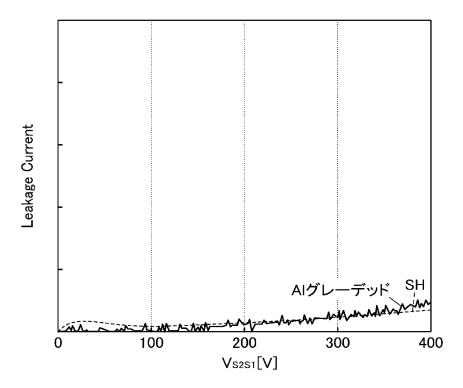

[図6]図6は、実施形態2に係る双方向スイッチ素子及び比較例に係る双方向スイッチ素子の電流-電圧特性図である。

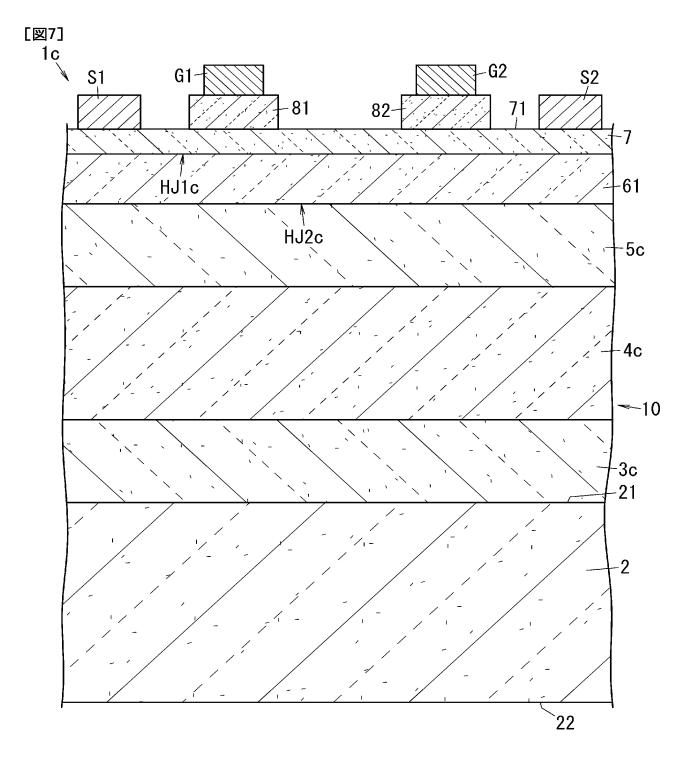

[図7]図7は、実施形態3に係る双方向スイッチ素子の断面図である。

# 発明を実施するための形態

- [0011] 下記の実施形態等において説明する図1、3、5及び7は、模式的な図であり、図1、3、5及び7中の各構成要素の大きさや厚さそれぞれの比が、必ずしも実際の寸法比を反映しているとは限らない。

- [0012] (実施形態1)

以下では、実施形態1に係る双方向スイッチ素子1について、図1に基づいて説明する。

- [0013] 双方向スイッチ素子1は、例えば、交流一交流電力変換を行うマトリクスコンバータ等の電力変換装置に使用可能であるが、これに限らず、例えば、リレー、照明装置の調光用の交流スイッチ等にも使用可能である。双方向スイッチ素子1は、例えば、デュアルゲート型のGaN系GIT (Gate Injection Transistor) である。

- [0014] 双方向スイッチ素子1は、基板2と、GaN層6と、第1のAIGaN層7と、第1のソース電極S1と、第1のゲート電極G1と、第2のゲート電極G2と、第2のソース電極S2と、第1のp型AIGaN層81と、第2のp型AIGaN層82と、を備える。

- [0015] GaN層6は、基板2上に形成されている。第1のAIGaN層7は、GaN層6上に形成されており、GaN層6と共に第1のヘテロ接合部HJ1を構成する。GaN層6においては、第1ヘテロ接合部HJ1の近傍に、2

次元電子ガス(Two-Dimensional Electron Gas)が発生している。 2次元電子ガスを含む領域(以下、「2次元電子ガス層」ともいう)は、 n チャネル層(電子伝導層)として機能することが可能である。

- [0016] 第1のソース電極S1は、第1のAIGaN層7上に形成されている。第1のゲート電極G1は、第1のAIGaN層7上に形成されている。第2のゲート電極G2は、第1のAIGaN層7上における、第1のゲート電極G1から見て第1のソース電極S1とは反対側の位置に形成されている。第2のソース電極S2は、第1のAIGaN層7上における、第2のゲート電極G2から見て第1のゲート電極G1とは反対側の位置に形成されている。ここにおいて、双方向スイッチ素子1では、第1のAIGaN層7の表面71に沿った一方向において、第1のソース電極S1、第1のゲート電極G1、第2のゲート電極G2及び第2のソース電極S2が、この順に並んでいる。第1のソース電極S1、第1のゲート電極G2及び第2のソース電極S1、第2のゲート電極G2及び第2のソース電極S1、第2のゲート電極G2及び第2のソース電極S1、第2のゲート電極G2及び第2のソース電極S2は、上記一方向において互いに離れている。

- [0017] 双方向スイッチ素子1は、ノーマリオフ型の双方向スイッチ素子であり、 上述の第1のp型AIGaN層81と、第2のp型AIGaN層82と、を 備えている。第1のp型AIGaN層81は、第1のゲート電極G1と第1 のAIGaN層7との間に介在している。第2のp型AIGaN層82は、 第2のゲート電極G2と第1のAIGaN層7との間に介在している。

- [0018] 以下では、説明の便宜上、第1のゲート電極G1と第1のソース電極S1との間に第1の閾値電圧以上の電圧が印加されていない状態を、第1のゲート電極G1がオフ状態ともいう。また、第1のゲート電極G1と第1のソース電極S1との間に第1のゲート電極G1を高電位側として第1の閾値電圧以上の電圧が印加されている状態を、第1のゲート電極G1がオン状態ともいう。また、第2のゲート電極G2と第2のソース電極S2との間に第2の閾値電圧以上の電圧が印加されていない状態を、第2のゲート電極G2がオフ状態ともいう。また、第2のゲート電極G2と第2のソース電極S2との間に第2のゲート電極G2を高電位側として第2の閾値電圧以上の電圧が印

加されている状態を、第2のゲート電極G2がオン状態ともいう。

- [0019] 双方向スイッチ素子1は、上述の第1のp型AIGaN層81及び第2のp型AIGaN層82を備えることにより、ノーマリオフ型のトランジスタを実現している。ここにおいて、第1のp型AIGaN層81は、第1のゲート電極G1がオフ状態のときに、第1のp型AIGaN層81は下において第1のAIGaN層7とGaN層6とに空乏層を形成する。第2のp型AIGaN層82は、第2のゲート電極G2がオフ状態のときに、第2のp型AIGaN層82は、第2のゲート電極G2がオフ状態のときに、第2のp型AIGaN層82は、第2のゲート電極G1がオン状態のときには、第1のゲート電極G1がオン状態のときには、第1のゲート電極G1と第1のソース電極S1との間を2次元電子ガスでつなげることができる(第1のゲート電極G1と第1のソース電極S1との間で2次元電子ガスが空乏層により遮られなくなる)。また、双方向スイッチ素子1では、第2のゲート電極G2がオン状態のときには、第2のゲート電極G2と第2のソース電極S2との間を2次元電子ガスでつなげることができる(第2のゲート電極G2と第2のソース電極S2との間を2次元電子ガスが空乏層により遮られなくなる)。

- [0020] 双方向スイッチ素子1では、第1のゲート電極G1がオフ状態で、かつ第2のゲート電極G2がオフ状態である場合(第1の動作モードの場合)、第1のソース電極S1と第2のソース電極S2との間において、いずれの方向にも電流を流すことができない。より詳細には、第1の動作モードの場合、第1のソース電極S1が第2のソース電極S2よりも高電位のときに第1のソース電極S1から第2のソース電極S2へ流れる電流が遮断され、かつ、第2のソース電極S2が第1のソース電極S1よりも高電位のときに第2のソース電極S2から第1のソース電極S1へ流れる電流が遮断される。

- [0021] 双方向スイッチ素子1では、第1のゲート電極G1がオン状態で、かつ第2のゲート電極G2がオン状態である場合(第2の動作モードの場合)、第1のソース電極S1と第2のソース電極S2との間において、双方向に電流を流すことができる。より詳細には、第2の動作モードの場合、第1のソー

ス電極S1が第2のソース電極S2よりも高電位のときに第1のソース電極S1から第2のソース電極S2へ電流が流れ、かつ、第2のソース電極S2が第1のソース電極S1よりも高電位のときに第2のソース電極S2から第1のソース電極S1へ電流が流れる。

- [0022] 双方向スイッチ素子1では、第1のゲート電極G1がオン状態で、かつ第2のゲート電極G2がオフ状態である場合(第3の動作モードの場合)、ダイオードとして機能する。より詳細には、第3の動作モードの場合、第1のソース電極S1が第2のソース電極S2よりも高電位のときには第1のソース電極S1から第2のソース電極S2へ流れる電流が遮断され、かつ、第2のソース電極S2が第1のソース電極S1よりも第2の閾値電圧以上、高電位のときには第2のソース電極S2から第1のソース電極S1へ電流が流れる。

- [0023] 双方向スイッチ素子1では、第1のゲート電極G1がオフ状態で、かつ第2のゲート電極G2がオン状態である場合(第4の動作モードの場合)、ダイオードとして機能する。より詳細には、第4の動作モードの場合、第2のソース電極S2が第1のソース電極S1よりも高電位のときには第2のソース電極S2から第1のソース電極S1へ流れる電流が遮断され、かつ、第1のソース電極S1が第2のソース電極S2よりも第1の閾値電圧以上、高電位のときには第1のソース電極S1から第2のソース電極S2へ電流が流れる。

- [0024] なお、双方向スイッチ素子1では、第1の閾値電圧と第2の閾値電圧とが同じ値であるが、互いの異なる値であってもよい。

- [0025] ところで、双方向スイッチ素子1は、第2のAIGaN層5と、第3のAIGaN層4と、を更に備える。第2のAIGaN層5は、基板2とGaN層6との間に位置しており、GaN層6と共に第2のヘテロ接合部HJ2を構成する。第3のAIGaN層4は、基板2と第2のAIGaN層5との間に位置している。

- [0026] 双方向スイッチ素子1は、基板2と第3のAIGaN層4との間に位置し

ているバッファ層3を更に備える。したがって、双方向スイッチ素子1は、バッファ層3と第3のAIGaN層4と第2のAIGaN層5とGaN層6と第1のAIGaN層7と第1のp型AIGaN層81及び第2のp型AIGaN層82とを含む積層体10を有している。

- [0027] 双方向スイッチ素子1の厚さ方向からの平面視における双方向スイッチ素子1の外周形状は、例えば、正方形状である。双方向スイッチ素子1の外周形状は、正方形状に限らず、例えば、長方形状等でもよい。

- [0028] 以下、双方向スイッチ素子1の各構成要素について、より詳細に説明する。

- Γ00297 基板2は、シリコン基板である。したがって、基板2は、導電性基板の一 種である。基板2は、第1主面21及び第2主面22を有する。基板2の第 1 主面21及び第2主面22は、基板2の厚さ方向に直交する。ここにおい て、「直交」とは、厳密に直交する場合のみに限定されず、略直交(厚さ方 向と第1主面21又は第2主面22とのなす角度が例えば90°±5°)で もよい。第2主面22は、基板2の厚さ方向において第1主面21の反対側 に位置している。双方向スイッチ素子1では、積層体10は、基板2の第1 主面21上に形成されている。基板2の第1主面21は、例えば、(111 ) 面である。基板2の第1主面21は、例えば、(111) 面からのオフ角 (以下、「第1オフ角」という)が0°よりも大きく5°以下の結晶面でも よい。ここにおいて、「第1オフ角」とは、(111)面に対する第1主面 21の傾斜角である。したがって、オフ角が0°であれば、第1主面21は 、(111)面である。(111)面は、3つの指数を括弧のなかに入れて 表記したミラー指数(Miller Index)による結晶面である。基板2の厚さは 、例えば、100μm以上1000μm以下である。

- [0030] 積層体10は、上述のように、バッファ層3と、第3のAIGaN層4と、第2のAIGaN層5と、GaN層6と、第1のAIGaN層7と、を含む。積層体10では、バッファ層3、第3のAIGaN層4、第2のAIGaN層5、GaN層6及び第1のAIGaN層7は、基板2側からこの順に

並んでいる。バッファ層3は、基板2上に直接形成されている。第3のAIGaN層4は、バッファ層3上に直接形成されている。第2のAIGaN層5は、第3のAIGaN層4上に直接形成されている。GaN層6は、第2のAIGaN層5上に直接形成されている。第1のAIGaN層7は、GaN層6上に直接形成されている。また、積層体10は、第1のAIGaN層7上に直接形成されている第1のp型AIGaN層81及び第2のp型AIGaN層82を含んでいる。

- [0031] 積層体 1 Oは、基板 2 上に例えばMOVPE(Metal Organic Vapor Phase Epitaxy)によって成長されたエピタキシャル成長層である。基板 2 上に積層体 1 Oを成長させるエピタキシャル成長装置としてMOVPE装置を採用する場合、A I の原料ガスとしては、トリメチルアルミニウム(T M A I)を採用するのが好ましい。また、G a の原料ガスとしては、トリメチルガリウム(T M G a)を採用するのが好ましい。Nの原料ガスとしては、N H  $_3$ を採用するのが好ましい。p型導電性に寄与する不純物であるM  $_3$ の原料ガスとしては、ビスシクロペンタジエニルマグネシウム(C  $_2$  M  $_3$  )を採用するのが好ましい。各原料ガスそれぞれのキャリアガスとしては、例えば、 $_3$  元を採用するのが好ましい。各原料ガスは、特に限定されず、例えば、G a の原料ガスとしてトリエチルガリウム(T E G a)、Nの原料ガスとしてヒドラジン誘導体を採用してもよい。

- [0032] バッファ層3は、例えば、アンドープのGaN層である。バッファ層3は、第3のAIGaN層4、第2のAIGaN層5、GaN層6、第1のAIGaN層7、第1のp型AIGaN層81及び第2のp型AIGaN層82の結晶性の向上を目的として設けた層である。バッファ層3は、基板2の第1主面21上に直接形成されている。バッファ層3を構成するアンドープのGaN層は、その成長時に不可避的に混入されるMg、H、Si、C、〇等の不純物が存在してもよい。バッファ層3の厚さは、例えば、100nm以上3000nm以下である。

- [0033] GaN層6は、アンドープのGaN層である。GaN層6を構成するアン

ドープのGaN層は、その成長時に不可避的に混入されるMg、H、Si、C、O等の不純物が存在してもよい。GaN層6の厚さは、例えば、100nm以上700nm以下である。

- [0034] 第1のAIGaN層7は、アンドープのAIGaN層である。上述のよう に、第1のAIGaN層7は、GaN層6と共に第1のヘテロ接合部HJ1 を構成する。GaN層6においては、第1ヘテロ接合部HJ1の近傍に、2 次元電子ガスが発生している。第1のAIGaN層7を構成するアンドープ のAIGaN層は、その成長時に不可避的に混入されるMg、H、Si、C 、〇等の不純物が存在してもよい。第1のAIGaN層7を構成するアンド ープのAIGaN層のAIの組成比は、例えば、O. 20である。本明細書 。Gao, 80 N層である。組成比は、例えば、EDX(Energy Dispersive X-ra y Spectroscopy) による組成分析で求めた値である。組成比の相対的な大小 関係を議論する上では、組成比は、EDXに限らず、例えば、オージェ電子 分光 (Auger Electron Spectroscopy) による組成分析、SIMSによる組成 分析で求めた値でもよい。実施形態1に係る双方向スイッチ素子1では、G a N層 6、第1のA I Ga N層 7、第1のp型A I Ga N層 8 1、第2のp 型AIGaN層82、第2のAIGaN層5及び第3のAIGaN層4が、 それぞれ、 $A \mid_z G a_{1-z} N \mathbb{B}$ (ここで、 $0 \le z < 1$ )、 $A \mid_b G a_{1-b} N \mathbb{B}$ ( ここで、0 < b < 1)、 $p 型 A \mid_{x_1} G a_{1-x_1} N 層 (ここで、<math>0 \le x 1 \le 1$ ) 、 p型A  $I_{\times 2}$  G a  $I_{-\times 2}$  N層(ここで、 0  $\leq$  x 2  $\leq$  1)、 A  $I_{\times}$  G a  $I_{-\times}$  N層( ここで、0 < y < 1、かつ、z < y < b)及び $A \mid_{w} G a_{1-w} N$ 層(ここで、 0 < w < 1、かつ、z < w < b)の一例である。

- [0035] 第1のAIGaN層7の厚さは、例えば、10nm以上100nm以下である。

- [0036] 第1のp型AIGaN層81及び第2のp型AIGaN層82は、第1の AIGaN層7の表面71の一部のみを覆っている。したがって、第1のA

IGaN層7の表面71は、第1のp型AIGaN層81及び第2のp型AIGaN層82に覆われている領域と、第1のp型AIGaN層81及び第2のp型AIGaN層82に覆われていない領域と、を含む。第1のp型AIGaN層81と第2のp型AIGaN層82とは、互いに離れている。第1のp型AIGaN層81及び第2のp型AIGaN層82は、その成長時にMgがドーピングされており、Mgを含有している。第1のp型AIGaN層81及び第2のp型AIGaN層82は、MOVPE装置によって第1のp型AIGaN層81と第2のp型AIGaN層82との元になるp型AIGaN層を第1のAIGaN層7上に成長させた後に、フォトリソグラフィ技術及びエッチング技術を利用してp型AIGaN層をパターニングすることによって形成されている。

- 第1のp型AIGaN層81のAIの組成比と第2のp型AIGaN層82のAIの組成比とは同じである。第1のp型AIGaN層81及び第2のp型AIGaN層82のAIの組成比は、第1のAIGaN層7のAIの組成比と同じ(例えば、O. 20)であるが、第1のAIGaN層7のAIの組成比と異なっていてもよい。第1のp型AIGaN層81及び第2のp型AIGaN層82の厚さは、例えば、50nm以上300nm以下である。

- [0038] 第1のソース電極S1及び第2のソース電極S2は、第1のAIGaN層7の表面71において第1のp型AIGaN層81及び第2のp型AIGaN層82に覆われていない領域に形成されている。第1のソース電極S1と第2のソース電極S2とは、互いに離れている。第1のソース電極S1及び第2のソース電極S2は、第1へテロ接合部HJ1と電気的に接続されている。ここにおいて、「電気的に接続されている」とはオーミック接触していることを意味する。第1のソース電極S1及び第2のソース電極S2の各々は、例えば、TiとAIとを含んでいる。

- [0039] 第1のゲート電極G1は、第1のp型AIGaN層81を介して第1のAIGaN層7上に形成されている。また、第2のゲート電極G2は、第2のp型AIGaN層82を介して第1のAIGaN層7上に形成されている。

第1のゲート電極G1と第2のゲート電極G2との距離は、第1のp型AIGaN層81と第2のp型AIGaN層82との距離よりも長い。第1のゲート電極G1及び第2のゲート電極G2の各々は、第1のAIGaN層7の表面71に沿った方向において、対応する第1のソース電極S1及び第2のソース電極S2それぞれから離れている。第1のゲート電極G1及び第2のゲート電極G2は、例えば、第1のp型AIGaN層81及び第2のp型AIGaN層82にそれぞれオーミック接触している。第1のゲート電極G1及び第2の及び第2のゲート電極G2の各々は、例えば、PdとAuとを含んでいる。

- [0040] 第2のAIGaN層5は、上述のように、GaN層6と共に第2のヘテロ接合部HJ2を構成する。第2のAIGaN層5は、GaN層6の厚さ方向において、第1のAIGaN層7側とは反対側に位置している。要するに、第2のAIGaN層5は、GaN層6を挟んで第1のAIGaN層7と対向している。したがって、双方向スイッチ素子1は、第1のAIGaN層7とGaN層6と第2のAIGaN層5とを含むダブルヘテロ構造を有している。第1のAIGaN層7及び第2のAIGaN層5の各々のバンドギャップは、GaN層6のバンドギャップよりも大きい。

- 第2のA | GaN層5は、アンドープのA | GaN層である。第2のA | GaN層5を構成するアンドープのA | GaN層は、その成長時に不可避的に混入されるMg、H、Si、C、O等の不純物が存在してもよい。第2のA | GaN層5のA | の組成比、言い換えれば、第2のA | GaN層5に対応するA | 、Ga<sub>1-</sub>、N層のA | の組成比yは、例えば、0.02である。つまり、第2のA | GaN層5は、アンドープのA | <sub>0.02</sub>Ga<sub>0.98</sub>N層である。第2のA | GaN層5を構成するA | 、Ga<sub>1-</sub>、N層のCの濃度は、一例として、7×10<sup>16</sup>cm<sup>-3</sup>であったが、この数値に限定されない。A | 、Ga<sub>1-</sub>、N層のCの濃度は、例えば、3×10<sup>17</sup>cm<sup>-3</sup>以下であるのが好ましい。Cの濃度は、S | MS(Secondary Ion Mass Spectroscopy)によって測定した値である。第2のA | GaN層5の厚さは、例えば、100 n m以上500 μ m以下である。

- [0042] 第3のAIGaN層4は、基板2と第2のAIGaN層5との間に位置し ている。第3のAIGaN層4のAIの組成比、言い換えれば、第3のAI GaN層4に対応するAlwGa1-wN層のAlの組成比wは、第2のAlG a N 層 5 の A I の組成比(第 2 の A I G a N 層 5 に対応する A I 、G a 1 - 、 N 層のAIの組成比y)と同じであるのが好ましく、例えば、〇. 〇2である 。つまり、第3のAIGaN層4は、Al<sub>0、02</sub>Ga<sub>0、98</sub>N層である。第3の AIGaN層4は、第2のAIGaN層5よりもCの濃度が高い。第3のA IGaN層4のCの濃度は、例えば、5×10<sup>18</sup>cm<sup>-3</sup>以上5×10<sup>19</sup>cm −3以下である。第3のAIGaN層4は、その成長時に意図的にCをドーピ ングしている。より詳細には、第3のAIGaN層4の成長速度が第2のA IGaN層5の成長速度よりも速くなるように第3のAIGaN層4の成長 条件を設定することにより、第3のAIGaN層4のCの濃度を第2のAI GaN層5のCの濃度よりも高くしている。ここにおいて、第3のAIGa N層4は、第2のAIGaN層5よりも電気絶縁性が高く、電気絶縁層とし て機能する。これにより、GaN層6の厚さ方向に電流が流れるのを抑制す ることができる。ここにおいて、第3のAIGaN層4の成長条件及び第2 のAIGaN層5の成長条件は、例えば、基板温度、V/III比、各原料ガス の供給量、成長圧力等を適宜設定すればよい。「基板温度」は、例えば、基 板2の元になるウェハを支持するサセプタ(susceptor)の温度を代用するこ とができる。例えば、基板温度は、熱電対により測定したサセプタの温度を 代用することができる。「V/III比」とは、III族元素の原料ガスのモル供 給量  $[\mu mol/min]$  に対するV族元素の原料ガスのモル供給量  $[\mu mol/min]$ の比である。「成長圧力」とは、各原料ガス及び各キャリアガスをMOVP E装置の反応炉内に供給している状態における反応炉内の圧力である。

- [0043] 第3のAIGaN層4の厚さは、第2のAIGaN層5の厚さよりも厚い のが好ましい。これにより、双方向スイッチ素子1の耐圧をより高くすることが可能となる。第3のAIGaN層4の厚さは、例えば、600nm以上 3000nm以下である。

- [0044] 本願発明者らは、実施形態1に係る双方向スイッチ素子1において、基板2を電気的にフローティングした状態で、双方向スイッチ素子1をターンオンさせたときのオン抵抗(Ron)の時間変化について評価した。ここにおいて、「基板2を電気的にフローティングした状態」とは、基板2が第1のソース電極S1、第2のソース電極S2、第1のゲート電極G1及び第2のゲート電極G2のいずれとも電気的に絶縁された状態を意味する。

- [0045] また、本願発明者らは、実施形態1に係る双方向スイッチ素子1の比較例に係る双方向スイッチ素子についても、基板をフローティングした状態で、比較例に係る双方向スイッチ素子をターンオンさせたときのオン抵抗の時間変化について評価した。比較例に係る双方向スイッチ素子は、実施形態1に係る双方向スイッチ素子1の第2のAIGaN層5を備えていない。比較例に係る双方向スイッチ素子は、実施形態1に係る双方向スイッチ素子1のGaN層6の代わりに、GaN層6の厚さと第2のAIGaN層5の厚さとの合計厚さを有する第1のGaN層を備え、第2のAIGaN層5よりもCの濃度の高い第3のAIGaN層4の代わりに、第1のGaN層よりもCの濃度の高い第2のGaN層を備えている。第1のGaN層は、アンドープのGaN層である。つまり、比較例に係る双方向スイッチ素子は、実施形態1に係る双方向スイッチ素子1のダブルヘテロ構造の代わりに、シングルヘテロ構造を採用している。

- [0046] オン抵抗の時間変化の評価に際しては、実施形態1に係る双方向スイッチ素子1及び比較例に係る双方向スイッチ素子それぞれに流れる電流の電流値を10Aとしたときのオン抵抗一時間特性により評価した。双方向スイッチ素子1及び比較例の双方向スイッチの各々の両端間(第1のソース電極S1と第2のソース電極S2との間)に接続している直流電源の電圧をVddとし、オン抵抗は、オームの法則に従ってVdd/10の計算で求めた値である。なお、双方向スイッチ素子1に関して、スイッチ動作させる前の電流コラプスの発生していない場合のオン抵抗の実測値は、30mΩである。

- [0047] 比較例の双方向スイッチ素子では、Vddが大きくなるほどオン抵抗が上

昇していることから、電流コラプスが発生していることが分かった。これに対して、実施形態1の双方向スイッチ素子1では、比較例の双方向スイッチ素子と比べて、Vddが大きくなった場合のオン抵抗の上昇が抑制されている。

- [0048] 図2A及び2Bは、実施形態1に係る双方向スイッチ素子1及び比較例の 双方向スイッチ素子それぞれについて、電流コラプスの発生していないとき のオン抵抗を1とした場合のオン抵抗の比(言い換えれば規格化されたオン 抵抗)とVddとの関係を示している。図2A及び2Bの各々は、基板2を 電気的にフローティングした状態でのオン抵抗の比とVddとの関係を示し ている。

- [0049] 図2A及び2Bからも、実施形態1の双方向スイッチ素子1では、比較例の双方向スイッチ素子と比べて、Vddが大きくなった場合のオン抵抗の上昇が抑制されていることが分かる。

- [0050] 実施形態1に係る双方向スイッチ素子1は、基板2と、GaN層6と、第1のAIGaN層7と、第1のソース電極S1と、第1のゲート電極G1と、第2のゲート電極G2と、第2のソース電極S2と、第1のp型AIGaN層81と、第2のp型AIGaN層82と、第2のAIGaN層5と、第3のAIGaN層4と、を備える。GaN層6は、基板2上に形成されている。第1のAIGaN層7は、GaN層6上に形成されている。第1のYース電極S1、第1のゲート電極G1、第2のゲート電極G2、及び、第2のソース電極S2は、第1のAIGaN層7上に形成されている。第1のp型AIGaN層81は、第1のゲート電極G1と第1のAIGaN層7との間に介在している。第2のp型AIGaN層82は、第2のゲート電極G2と第1のAIGaN層7との間に介在している。第2のAIGaN層5は、基板2とGaN層6との間に介在している。第3のAIGaN層4は、基板2と第2のAIGaN層5との間に介在し、第2のAIGaN層5よりもCの濃度が高い。

- [0051] 実施形態 1 に係る双方向スイッチ素子 1 では、上記の第2のA I G a N 層

5及び第3のAIGaN層4を備えることにより、電流コラプスを抑制することが可能となる。

- [0052] 図3は、実施形態1の変形例に係る双方向スイッチ素子1aの断面図である。変形例に係る双方向スイッチ素子1aに関し、実施形態1に係る双方向スイッチ素子1と同様の構成要素については、同一の符号を付して説明を省略する。

- [0053] 変形例に係る双方向スイッチ素子1 a は、実施形態1 に係る双方向スイッチ素子1 の第3のA | GaN層4、第2のA | GaN層5の代わりに、第3のA | GaN層4 a、第2のA | GaN層5 aを備えている。第3のA | GaN層4 a N層4 a は、アンドープのA | GaN層である。第3のA | GaN層4 a のA | の組成比は、O. O5である。つまり、第3のA | GaN層4 a は、アンドープのA | 0.05 Ga 0.95 N層である。また、第3のA | GaN層4 a の A | の組成比は、第3のA | GaN層4 a の A | の組成比は、第3のA | GaN層4 a の A | の組成比と同じであり、O. O5である。

- [0054] 第2のA | GaN層5 aは、基板2とGaN層6との間に位置しており、GaN層6と共に第2のヘテロ接合部HJ2を構成する。第3のA | GaN層4 aは、基板2と第2のA | GaN層5 aとの間に位置しており、第2のA | GaN層5 aよりもCの濃度が高い。第2のA | GaN層5 aを構成するアンドープのA | GaN層0Cの濃度は、一例として、 $7 \times 10^{16} \, \mathrm{cm}^{-3}$ である。第3のA | GaN層4 aのCの濃度は、例えば、 $5 \times 10^{18} \, \mathrm{cm}^{-3}$ 以上 $5 \times 10^{19} \, \mathrm{cm}^{-3}$ 以下である。実施形態1の変形例に係る双方向スイッチ素子1 aでは、GaN層6、第1のA | GaN層7、第1のp型A | GaN層81、第2のp型A | GaN層82、第2のA | GaN層5 a及び第3のA | GaN層4 aが、それぞれ、A |  $_z$  Ga $_{1-z}$  N層(ここで、 $0 \le z < 1$ )、A |  $_b$  Ga $_{1-b}$  N層(ここで、0 < b < 1)、p型A |  $_{x1}$  Ga $_{1-x1}$  N層(ここで、 $0 \le x 2 \le 1$ )、A |  $_y$  Ga $_{1-y}$  N層(ここで、0 < w < 1、かつ、z < w < b)の一例である。

- [0055] 変形例に係る双方向スイッチ素子1aは、実施形態1に係る双方向スイッチ素子1と同様、電流コラプスの発生を抑制することが可能となる。

- [0056] ここにおいて、変形例に係る双方向スイッチ素子1では、比較例に係る双方向スイッチ素子と比べてオフリーク電流が大きくなってしまう。これに対して、実施形態1に係る双方向スイッチ素子1では、変形例に係る双方向スイッチ素子と比べてオフリーク電流を低減することができる。オフリーク電流とは、第1のゲート電極G1がオフ状態、第2のゲート電極G2がオフ状態のときに、第2のソース電極S2から第1のソース電極S1へ流れる電流である。

- [0057] 図4は、第2のソース電極S2を第1のソース電極S1よりも高電位として第2のソース電極S2と第1のソース電極S1との間の電圧を $V_{s2S1}$ とした場合の、 $V_{s2S1}$ とリーク電流(オフリーク電流)との関係を示している。図4中のDHは、上述のダブルへテロ構造を有する実施形態1の双方向スイッチ素子1の一例の測定データであり、図4中のSHは上述のシングルへテロ構造を有する比較例の双方向スイッチ素子の一例の測定データである。図4から、 $V_{s2S1}$ が400V以下であれば、実施形態1に係る双方向スイッチ素子1のリーク電流が比較例の双方向スイッチのリーク電流よりも小さいことが分かる。

- [0058] 上述のように実施形態1に係る双方向スイッチ素子1は、第2のAIGaN層5のAIの組成比が0.05未満である。これにより、実施形態1に係る双方向スイッチ素子1は、オフリーク電流を抑制することが可能となる。

- [0059] (実施形態2)

以下では、実施形態2に係る双方向スイッチ素子1bについて、図5に基づいて説明する。

- [0060] 実施形態2に係る双方向スイッチ素子1bに関し、実施形態1に係る双方向スイッチ素子1(図1参照)と同様の構成要素については、同一の符号を付して説明を省略する。

- [0061] 実施形態2に係る双方向スイッチ素子1bは、実施形態1に係る双方向ス

イッチ素子1の第3のA | GaN層4、第2のA | GaN層5の代わりに、第3のA | GaN層4 b、第2のA | GaN層5 bを備えている。実施形態2に係る双方向スイッチ素子1 bでは、GaN層6、第1のA | GaN層7、第1のp型A | GaN層81、第2のp型A | GaN層82、第2のA | GaN層5 b及び第3のA | GaN層4 bが、それぞれ、A |  $_z$ Ga $_{1-z}$ N層(ここで、0 $\le$ z<1)、A |  $_b$ Ga $_{1-b}$ N層(ここで、0<b<1)、p型A |  $_{x_1}$ Ga $_{1-x_1}$ N層(ここで、0 $\le$ x $1<math>\le$ 1)、p型A |  $_{x_2}$ Ga $_{1-x_2}$ N層(ここで、0 $\le$ x1 $\le$ 1)、A |  $_y$ Ga $_{1-y}$ N層(ここで、0<y<1、かつ、z<y<b)及びA |  $_y$ Ga $_{1-w}$ N層(ここで、0<w<1、かつ、z<w<b)の一例である。

- [0062] 第3のAIGaN層4bのAIの組成比は、例えば、O. O5である。つまり、第3のAIGaN層4bは、AI<sub>0. 05</sub>Ga<sub>0. 95</sub>N層である。第3のAIGaN層4bは、第2のAIGaN層5bよりもCの濃度が高い。第3のAIGaN層4bのCの濃度は、例えば、1×10<sup>19</sup>cm<sup>-3</sup>以上1×10<sup>19</sup>cm<sup>-3</sup>以下である。

- [0063] 第2のAIGaN層5bのAIの組成比は、第3のAIGaN層4bのAIの組成比よりも小さい。第2のAIGaN層5bでは、第2のAIGaN層5bのAIGaN層5bのAIGaN層5bのAIGaN層5bのFみ方向において第3のAIGaN層4bから離れるにつれてAIの組成比が小さくなっている。言い換えれば、第2のAIGaN層5bは、第3のAIGaN層4bから離れるにつれてバンドギャップエネルギが小さくなっており、GaN層6に近づくにつれてGaN層6とのバンドギャップエネルギの差が小さくなっている。ここにおいて、第2のAIGaN層5bは、例えば、互いにAIの組成比の異なる3層以上のAIGaN層の積層膜である。一例として、第2のAIGaN層5bは、互いにAIの組成比の異なる10層のAIGaN層の積層膜である。ここにおいて、10層のAIGaN層の各々の厚さは、第2のAIGaN層5bの厚さの10分の1の厚さである。また、10層のAIGaN層は、第2のAIGaN層5bの厚み方向においてGaN層6から離れるにつれてAIの組成比が0.005ずつ増

加している。つまり、10層のAIGaN層は、第2のAIGaN層5bの厚み方向においてGaN層6側から、AI<sub>0.005</sub>Ga<sub>0.995</sub>N層、AI<sub>0.01</sub>Ga<sub>0.99</sub>N層、AI<sub>0.01</sub>Ga<sub>0.98</sub>N層、AI<sub>0.02</sub>Ga<sub>0.98</sub>N層、AI<sub>0.02</sub>Ga<sub>0.98</sub>N層、AI<sub>0.02</sub>Ga<sub>0.98</sub>N層、AI<sub>0.02</sub>Ga<sub>0.98</sub>N層、AI<sub>0.03</sub>Ga<sub>0.96</sub>N層、AI<sub>0.04</sub>Ga<sub>0.96</sub>N層、AI<sub>0.04</sub>Ga<sub>0.95</sub>N層、AI<sub>0.05</sub>Ga<sub>0.95</sub>N

- [0064] 実施形態2に係る双方向スイッチ素子1bは、実施形態1に係る双方向スイッチ素子1と同様、電流コラプスの発生を抑制することが可能となる。

- [0065] 図6は、 $V_{S2S1}$ とリーク電流(オフリーク電流)との関係を示している。図6中のA I グレーデッドは実施形態 2 に係る双方向スイッチ素子 1 bの一例の測定データであり、図6中のS Hは上述のシングルへテロ構造を有する比較例の双方向スイッチ素子の一例の測定データである。図6から、 $V_{S2S1}$ が250 V以下であれば、実施形態 2 に係る双方向スイッチ素子 1 bのリーク電流が比較例の双方向スイッチのオフリーク電流よりも小さいことが分かる。

- [0066] (実施形態3)

以下では、実施形態3に係る双方向スイッチ素子1 c について、図7に基づいて説明する。

- [0067] 実施形態3に係る双方向スイッチ素子1cに関し、実施形態1に係る双方向スイッチ素子1(図1参照)と同様の構成要素については、同一の符号を付して説明を省略する。

- [0068] 実施形態3に係る双方向スイッチ素子1 c は、実施形態1に係る双方向スイッチ素子1のバッファ層3、第3のA | G a N層4、第2のA | G a N層 5及びG a N層6の代わりに、バッファ層3 c 、第3のA | G a N層4 c 、第2のA | G a N層5 c 及び第4のA | G a N層61を備えている。実施形態3に係る双方向スイッチ素子1 c では、第4のA | G a N層61、第1のA | G a N層7、第1のp型A | G a N層81、第2のp型A | G a N層82、第2のA | G a N層5 c 及び第3のA | G a N層4 c が、それぞれ、A | z G a 1-z N層(ここで、0≤z<1)、A | b G a 1-b N層(ここで、0<

b < 1)、 $p 型 A I_{x1} G a_{1-x1} N \overline{B}$ (ここで、 $0 \le x 1 \le 1$ )、 $p 型 A I_{x2} G a_{1-x2} N \overline{B}$ (ここで、 $0 \le x 2 \le 1$ )、 $A I_y G a_{1-y} N \overline{B}$ (ここで、0 < y < 1、かつ、z < y < b)及び $A I_w G a_{1-w} N \overline{B}$ (ここで、0 < w < 1、かつ、z < w < b)の一例である。

- [0069] 第4のAIGaN層61は、アンドープのAIGaN層である。第4のAIGaN層61を構成するアンドープのAIGaN層は、その成長時に不可避的に混入されるMg、H、Si、C、O等の不純物が存在してもよい。第4のAIGaN層61の厚さは、例えば、100nm以上700nm以下である。第4のAIGaN層61に対応するAI<sub>z</sub>Ga<sub>1-z</sub>N層のAIの組成比zが、第1のAIGaN層7により構成されるAI<sub>b</sub>Ga<sub>1-b</sub>N層のAIの組成比成比りよりも小さく、かつ、第2のAIGaN層5cに対応するAI<sub>y</sub>Ga<sub>1-</sub>、N層のAIの組成比yよりも小さい。

- [0070] 第1のAIGaN層7は、第4のAIGaN層61と共に第1のヘテロ接合部HJ1cを構成する。第4のAIGaN層61においては、第1ヘテロ接合部HJ1cの近傍に、2次元電子ガスが発生している。第1のAIGaN層7を構成するアンドープのAIGaN層のAIの組成比は、例えば、0.17である。

- [0071] 第2のA | GaN層5 cは、第4のA | GaN層6 1 と共に第2のヘテロ接合部H J 2 cを構成する。第2のA | GaN層5 cは、第4のA | GaN層6 1 の厚さ方向において、第1のA | GaN層7 側とは反対側に位置している。要するに、第2のA | GaN層5 cは、第4のA | GaN層6 1 を挟んで第1のA | GaN層7 と対向している。したがって、双方向スイッチ素子1 cは、第1のA | GaN層7 と第4のA | GaN層6 1 と第2のA | GaN層5 cとを含むダブルヘテロ構造を有している。第1のA | GaN層7 及び第2のA | GaN層5 cの各々のバンドギャップは、第4のA | GaN層6 1 のバンドギャップよりも大きい。

- [0072] 第2のA | GaN層5cは、アンドープのA | GaN層である。第2のA | GaN層5cを構成するアンドープのA | GaN層は、その成長時に不可

避的に混入されるMg、H、Si、C、O等の不純物が存在してもよい。第 2のAlGaN層5cのAlの組成比、言い換えれば、第2のAlGaN層5cに対応するAl $_y$ Ga $_{1-y}$ N層のAlの組成比yは、例えば、0. 02である。つまり、第2のAlGaN層5cは、アンドープのAl $_{0.02}$ Ga $_{0.98}$ N層である。第2のAlGaN層5cに対応するAl $_y$ Ga $_{1-y}$ N層のCの濃度は、一例として、 $7 \times 1$  Olecm-3であったが、この数値に限定されない。Al $_y$ Ga $_{1-y}$ N層のCの濃度は、例えば、 $3 \times 1$  Olecm-3以下であるのが好ましい。第2のAlGaN層5cの厚さは、例えば、100nm以上500 $\mu$ m以下である。

- Γ0073] 第3のAIGaN層4cは、基板2と第2のAIGaN層5cとの間に位 置している。第3のAIGaN層4cのAIの組成比、言い換えれば、第3 のAIGaN層4cにより構成されるAI、Ga1-、N層のAIの組成比wは 、第2のAIGaN層5cに対応するAI<sub>ν</sub>Ga<sub>1-ν</sub>N層のAIの組成比yと 同じであるのが好ましく、例えば、〇. 〇2である。つまり、第3のAIG aN層4cは、Alogo2Gaog8N層である。第3のAlGaN層4cは、 第2のAIGaN層5cよりもCの濃度が高い。第3のAIGaN層4cの Cの濃度は、例えば、 $5 \times 10^{18} \text{ cm}^{-3}$ 以上 $5 \times 10^{19} \text{ cm}^{-3}$ 以下である。 第3のAIGaN層4cは、その成長時に意図的にCをドーピングしている 。より詳細には、第3のAIGaN層4cの成長速度が第2のAIGaN層 5cの成長速度よりも速くなるように第3のAIGaN層4cの成長条件を 設定することにより、第3のAIGaN層4cのCの濃度を第2のAIGa N層5cのCの濃度よりも高くしている。ここにおいて、第3のAIGaN 層4cは、第2のAIGaN層5cよりも電気絶縁性が高く、電気絶縁層と して機能する。これにより、第4のAIGaN層61の厚さ方向に電流が流 れるのを抑制することができる。

- [0074] バッファ層3 c は、C ドープのG a N層である。バッファ層3 c は、その成長時に意図的にCをドーピングしている。バッファ層3 c のC の濃度は、アンドープのG a N層により構成されるバッファ層3 のC の濃度よりも高い

- 。バッファ層3cの厚さは、例えば、100nm以上3000nm以下である。

- [0075] 実施形態3に係る双方向スイッチ素子1 c は、第2のA l G a N 層5 c に対応するA l  $_y$  G a  $_{1-y}$  N 層のA l の組成比 y が O . O 5 未満である。これにより、実施形態3に係る双方向スイッチ素子1 c は、オフリーク電流を抑制することが可能となる。

- [0076] また、実施形態3に係る双方向スイッチ素子1 c は、第3のA | G a N層 4 c に対応するA |  $_w$ G a  $_{1-w}$ N層のA | の組成比wが0.05未満である。これにより、実施形態3に係る双方向スイッチ素子1 c は、オフリーク電流を抑制することが可能となる。

- [0077] また、実施形態3に係る双方向スイッチ素子1 c は、第2のA | G a N 層 5 c に対応するA | <sub>y</sub> G a <sub>1-y</sub> N 層のA | の組成比 y が O . O 3 未満であり、第3のA | G a N 層 4 c に対応するA | <sub>w</sub> G a <sub>1-w</sub> N 層のA | の組成比 w が O . O 3 未満であるのが好ましい。これにより、実施形態3に係る双方向スイッチ素子1 c では、オフリーク電流をより一層抑制することが可能となる。

- [0078] 上記の実施形態 1 ~ 3 等は、本開示の様々な実施形態の一つに過ぎない。 上記の実施形態 1 ~ 3 等は、本開示の目的を達成できれば、設計等に応じて 種々の変更が可能である。

- [0079] 例えば、第2のAIGaN層5bにおける3層以上のAIGaN層の厚さの関係は、特に限定されない。例えば、3層以上のAIGaN層は、厚さが同じである場合に限らず、互いに厚さが異なっていてもよい。

- [0080] また、第2のAIGaN層5bは、AIの組成比がステップ状に変化している場合に限らず、連続的に変化していてもよい。

- [0081] また、基板2は、シリコン基板に限らず、例えば、GaN基板、SiC基板、サファイア基板等であってもよい。

- [0082] 双方向スイッチ素子1、1 a、1 b、1 c の各々の他の第1例では、第1 のp型A | G a N層81の代わりに第1のp型G a N層を備え、第2のp型 A | G a N層82の代わりに第2のp型G a N層を備えていてもよい。

- Γ00837 また、双方向スイッチ素子1、1a、1b、1cの各々の他の第2例では 、第1のp型AIGaN層81の代わりに、p型金属酸化物半導体層からな る第1のゲート層を備え、第2のp型AIGaN層の代わりに、p型金属酸 化物半導体層からなる第2のゲート層を備えていてもよい。第1のゲート層 及び第2のゲート層の各々のp型金属酸化物半導体層は、例えば、NiO層 である。NiO層は、例えば、リチウム、ナトリウム、カリウム、ルビジウ ム及びセシウムの群から選ばれる少なくとも1種のアルカリ金属を不純物と して含んでいてもよい。また、NiO層は、例えば、不純物として添加され たときに一価となる銀、銅等の遷移金属を含んでいてもよい。第1のゲート 層は、第1のゲート電極G1と第1のソース電極S1との間に電圧が印加さ れていないときに、第1のゲート層直下において第1のAIGaN層7とG aN層6とに空乏層を形成する。第2のゲート層は、第2のゲート電極G2 と第2のソース電極S2との間に電圧が印加されていないときに、第2のゲ ート層直下において第1のA | GaN層7とGaN層6とに空乏層を形成す る。

- [0084] また、双方向スイッチ素子 1 の他の第 3 例では、第 2 の A | G a N 層 5 の 代わりに、 | n A | G a N 層を備えていてもよい。この場合、 | n A | G a N 層は、アンドープの | n a 05 A | a 16 G a a 85 N 層により構成してもよい。

- [0085] また、双方向スイッチ素子 1 の他の第 4 例では、第 3 の A I G a N 層 4 の 代わりに、I n A I G a N 層を備えていてもよい。この場合、第 3 の A I G a N 層 4 の代わりの I n A I G a N 層 は、第 2 の A I G a N 層 5 の代わりの I n A I G a N 層よりも C の濃度の高い I n<sub>0.05</sub> A I<sub>0.10</sub> G a<sub>0.85</sub> N 層により構成 してもよい。

- [0086] (まとめ)

以上説明した実施形態等から本明細書には以下の態様が開示されている。

[0087] 第1の態様に係る双方向スイッチ素子(1;1a;1b;1c)は、基板

(2)と、A I z G a 1-z N層(ここで、0≤z < 1)と、A I b G a 1-b N層</li>

(ここで、0<b<1)と、第1のソース電極(S1)と、第1のゲート電</li>

極(G1)と、第2のゲート電極(G2)と、第2のソース電極(S2)と 、p型A I <sub>×1</sub> G a <sub>1-×1</sub> N層(ここで、0≦×1≦1)と、p型A I <sub>×2</sub> G a <sub>1-</sub> <sub>x2</sub>N層(ここで、0≦x2≦1)と、Al<sub>y</sub>Ga<sub>1-y</sub>N層(ここで、0<y< 1、かつ、z < y < b)と、 $A \mid_{w} G a_{1-w} N$ 層(ここで、0 < w < 1、かつ 、z < w < b )と、を備える。A I <sub>z</sub> G a <sub>1-z</sub> N層(G a N層 6 ; 第 4 の A I GaN層61) は、基板(2)上に形成されている。 $AI_bGa_{1-b}N層$ (第 1のAIGaN層7)は、AIzGa1-zN層(GaN層6;第4のAIGa N層61)上に形成されている。第1のソース電極(S1)、第1のゲート 電極(G1)、第2のゲート電極(G2)、及び、第2のソース電極(S2) )は、AIϧGaューϧN層(第1のAIGaN層7)上に形成されている。p 型 $A \mid_{x_1} G a_{1-x_1} N$ 層(第1 o p型 $A \mid G a N$ 層8 1)は、第1 o f 一ト電 極(G1)とAI<sub>b</sub>Ga<sub>1-b</sub>N層(第1のAIGaN層7)との間に介在して いる。p型AI<sub>x2</sub>Ga<sub>1-x2</sub>N層(第2のp型AIGaN層82)は、第2の ゲート電極 (G2) と $A \mid_b Ga_{1-b} N$ 層 (第1の $A \mid GaN$ 層7) との間に 介在している。AI、Ga<sub>1-</sub>、N層(第2のAIGaN層5;5a;5b;5 c) は、基板(2)とAI、GaI-、N層(GaN層6;第4のAIGaN層 61) との間に介在している。A I "G a 1- "N層(第3のA I G a N層4; 4 a; 4 b; 4 c) は、基板(2)とAI、Ga1-、N層(第2のAIGaN 層5;5a;5b;5c)との間に介在し、Al、Ga<sub>1-</sub>、N層(第2のAl **GaN層5**; **5a**; **5b**; **5c**) よりも**C**の濃度が高い。

- [0088] 第1の態様に係る双方向スイッチ素子(1;1a;1b;1c)では、電流コラプスを抑制することが可能となる。

- [0089] 第2の態様に係る双方向スイッチ素子(1;1c)では、第1の態様において、Al<sub>y</sub>Ga<sub>1-y</sub>N層(第2のAlGaN層5;5c)のAlの組成比(y)がO. O5未満である。

- [0090] 第2の態様に係る双方向スイッチ素子(1;1c)では、オフリーク電流 を抑制することが可能となる。

- [0091] 第3の態様に係る双方向スイッチ素子(1b)では、第1又は2の態様に

おいて、 $A I_y G a_{1-y} N \overline{B}$  (第2の $A I G a N \overline{B} 5 b$ ) のA I の組成比(y )は、 $A I_w G a_{1-w} N \overline{B}$  (第3の $A I G a N \overline{B} 4 b$ ) のA I の組成比(w) よりも小さい。 $A I_y G a_{1-y} N \overline{B}$  (第2の $A I G a N \overline{B} 5 b$ ) では、 $A I_y G a_{1-y} N \overline{B}$  (第2の $A I G a N \overline{B} 5 b$ ) の $\overline{B}$  の $\overline{B}$  から離れるにつれてA I O が小さくなっている。

- [0092] 第3の態様に係る双方向スイッチ素子(1b)では、オフリーク電流を抑制することが可能となる。

- [0093] 第4の態様に係る双方向スイッチ素子(1b)では、第 $1\sim3$ の態様のいずれか一つにおいて、 $A \mid_y Ga_{1-y} N$ 層(第2の $A \mid GaN$ 層5b)は、互いに $A \mid$  の組成比の異なる3層以上の $A \mid GaN$ 層の積層膜である。

- [0094] 第4の態様に係る双方向スイッチ素子(1b)では、オフリーク電流の発生を抑制することが可能となる。

- [0095] 第5の態様に係る双方向スイッチ素子(1 c)では、第2の態様において、AI<sub>w</sub>Ga<sub>1-w</sub>N層(第3のAIGaN層4 c)のAIの組成比(w)がO

. 05未満である。

- [0096] 第5の態様に係る双方向スイッチ素子(1c)では、オフリーク電流をより抑制することが可能となる。

- [0097] 第6の態様に係る双方向スイッチ素子(1 c)では、第5の態様において、Al<sub>y</sub>Ga<sub>1-y</sub>N層(第2のAlGaN層5 c)のAlの組成比(y)が0.03未満であり、Al<sub>w</sub>Ga<sub>1-w</sub>N層(第3のAlGaN層4 c)のAlの組成比(w)が0.03未満である。

- [0098] 第6の態様に係る双方向スイッチ素子(1c)では、オフリーク電流をより一層抑制することが可能となる。

- [0099] 第7の態様に係る双方向スイッチ素子(1;1a;1b;1c)は、第1 ~6の態様のいずれか一つにおいて、基板(2)が第1のソース電極(S1)、第2のソース電極(S2)、第1のゲート電極(G1)及び第2のゲート電極(G2)のいずれとも電気的に絶縁された状態で使用される。

- [0100] 第7の態様に係る双方向スイッチ素子(1;1a;1b;1c)では、基板(2)が接地された状態で使用することなく電流コラプスを抑制することが可能となる。

- [0101] 第8の態様に係る双方向スイッチ素子(1;1a;1b;1c)では、第 1~7の態様のいずれか一つにおいて、第3のAIGaN層(4;4a;4 b;4c)の厚さが、第2のAIGaN層(5;5a;5b;5c)の厚さ よりも厚い。

- [0102] 第8の態様に係る双方向スイッチ素子(1;1a;1b;1c)では、耐圧の向上を図ることが可能となる。

# 符号の説明

- [0103] 1、1a、1b、1c 双方向スイッチ素子

- 2 基板

- 4、4a、4b、4c 第3のAIGaN層(AI, Ga<sub>1-w</sub>N層)

- 5、5a、5b、5c 第2のAIGaN層(AI、Ga1-、N層)

- 6 GaN層(Al, Ga<sub>1-z</sub>N層)

- 61 第4のAIGaN層(AI, Ga<sub>1-1</sub>N層)

- 7 第1のAIGaN層(AI<sub>h</sub>Ga<sub>1-h</sub>N層)

- 81 第1のp型AIGaN層(p型AIx1Ga1-x1N層)

- 82 第2のp型AIGaN層(p型AI<sub>x2</sub>Ga<sub>1-x2</sub>N層)

- G1 第1のゲート電極

- G2 第2のゲート電極

- S1 第1のソース電極

- S2 第2のソース電極

# 請求の範囲

[請求項1] 基板と、

前記基板上に形成されている A  $I_z$  G a  $I_{z}$  N 層(ここで、 O  $\leq$  z < 1 )と、

前記 $A \mid_z G a_{1-z} N$ 層上に形成されている $A \mid_b G a_{1-b} N$ 層(ここで、0 < b < 1)と、

前記 $A I_b G a_{1-b} N$ 層上に形成されている第1のソース電極、第1のゲート電極、第2のゲート電極、及び、第2のソース電極と、

前記第1のゲート電極と前記 $A \mid_b G a \mid_{-b} N$ 層との間に介在しているp型 $A \mid_{x_1} G a \mid_{-x_1} N$ 層(ここで、 $O \le x \mid_{x_1} 1 \le 1$ )と、

前記第2のゲート電極と前記 $A \mid_b G a_{1-b} N$ 層との間に介在しているp型 $A \mid_{x2} G a_{1-x2} N$ 層(ここで、 $O \le x 2 \le 1$ )と、

前記基板と前記 $A \mid_z G a \mid_{-z} N$ 層との間に介在している $A \mid_y G a \mid_{-y} N$ 層(ここで、0 < y < 1、かつ、z < y < b)と、

前記基板と前記 $A \mid_y G a_{1-y} N$ 層との間に介在し、前記 $A \mid_y G a_{1-y} N$ 層よりもCの濃度が高い $A \mid_w G a_{1-w} N$ 層(ここで、O < w < 1、かつ、z < w < b)と、を備える、

双方向スイッチ素子。

[請求項2] 前記AI<sub>y</sub>Ga<sub>1-y</sub>N層のAIの組成比yがO. O5未満である、請求項1に記載の双方向スイッチ素子。

[請求項3] 前記AI<sub>y</sub>Ga<sub>1-y</sub>N層のAIの組成比yは、前記AI<sub>w</sub>Ga<sub>1-w</sub>N 層のAIの組成比wよりも小さく、

前記 $A \mid_y G a_{1-y} N$ 層では、前記 $A \mid_y G a_{1-y} N$ 層の厚み方向において前記 $A \mid_w G a_{1-w} N$ 層から離れるにつれて $A \mid$  の組成比y が小さくなっている、

請求項1又は2に記載の双方向スイッチ素子。

[請求項4] 前記Al<sub>y</sub>Ga<sub>1-y</sub>N層は、互いにAlの組成比の異なる3層以上のAlGaN層の積層膜である、

請求項1~3のいずれか一項に記載の双方向スイッチ素子。

[請求項5] 前記AI、Ga1-、N層のAIの組成比wがO. O5未満である、

請求項2に記載の双方向スイッチ素子。

[請求項6] 前記AI、Ga1-、N層のAIの組成比yがO. O3未満であり、

前記AI<sub>w</sub>Ga<sub>1-w</sub>N層のAIの組成比wがO. O3未満である、

請求項5に記載の双方向スイッチ素子。

[請求項7] 前記基板が前記第1のソース電極、前記第2のソース電極、前記第

1のゲート電極及び前記第2のゲート電極のいずれとも電気的に絶縁

された状態で使用される、

請求項1~6のいずれか一項に記載の双方向スイッチ素子。

[請求項8] 前記AIwGa1-wN層の厚さが、前記AIvGa1-vN層の厚さよ

りも厚い、

請求項1~7のいずれか一項に記載の双方向スイッチ素子。

[図6]

### INTERNATIONAL SEARCH REPORT

International application No.

PCT/JP2019/023188

1994-2019

### A. CLASSIFICATION OF SUBJECT MATTER

H01L21/338(2006.01)i, C30B29/38(2006.01)i, H01L21/337(2006.01)i, H01L21/365(2006.01)i, H01L29/778(2006.01)i, H01L29/808(2006.01)i, Int.Cl. H01L29/812(2006.01)i

According to International Patent Classification (IPC) or to both national classification and IPC

#### B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

Int.Cl. H01L21/338, C30B29/38, H01L21/337, H01L21/365, H01L29/778, H01L29/808, H01L29/812

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched Published examined utility model applications of Japan 1922-1996 Published unexamined utility model applications of Japan 1971-2019 Registered utility model specifications of Japan 1996-2019 Published registered utility model applications of Japan

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

#### C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                              | Relevant to claim No. |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Y<br>A    | JP 2015-115582 A (RENESAS ELECTRONICS CORP.) 22<br>June 2015, paragraphs [0017]-[0120], fig. 1-3 & US<br>2015/0171204 A1, paragraphs [0058]-[0161], fig. 1-<br>3 & EP 2884539 A1 & CN 104716176 A & KR 10-2015-<br>0070001 A & TW 201528503 A   | 1-4, 8<br>5-7         |

| Y<br>A    | JP 2017-521869 A (TRANSPHORM INC.) 03 August 2017, paragraphs [0004], [0088]-[0092], [0106]-[0115], fig. 1, 10, 14F & US 2016/0020313 A1, paragraphs [0005], [0104]-[0108], [0123]-[0131], fig. 1, 10, 14F & WO 2016/014439 A1 & CN 106537560 A | 1-4, 8<br>5-7         |

|                                      | Further documents are listed in the continuation of Box C.                                           | See patent family annex.                                                                                                               |  |  |

|--------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|

| *                                    | Special categories of cited documents:                                                               | "T" later document published after the international filing date or priority                                                           |  |  |

| "A"                                  | document defining the general state of the art which is not considered to be of particular relevance | date and not in conflict with the application but cited to understand<br>the principle or theory underlying the invention              |  |  |

| "E"                                  | earlier application or patent but published on or after the international filing date                | "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive |  |  |

| "L"                                  | document which may throw doubts on priority claim(s) or which is                                     | step when the document is taken alone                                                                                                  |  |  |

|                                      | cited to establish the publication date of another citation or other special reason (as specified)   | "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is     |  |  |

| "O"                                  | document referring to an oral disclosure, use, exhibition or other means                             | combined with one or more other such documents, such combination                                                                       |  |  |

| "P"                                  | document published prior to the international filing date but later than                             | being obvious to a person skilled in the art  "&" document member of the same patent family                                            |  |  |

|                                      | the priority date claimed                                                                            | a document member of the same patent ranning                                                                                           |  |  |

| Date                                 | of the actual completion of the international search                                                 | Date of mailing of the international search report                                                                                     |  |  |

| 07 August 2019 (07.08.2019)          |                                                                                                      | 20 August 2019 (20.08.2019)                                                                                                            |  |  |

|                                      |                                                                                                      |                                                                                                                                        |  |  |

| Name and mailing address of the ISA/ |                                                                                                      | Authorized officer                                                                                                                     |  |  |

| Japan Patent Office                  |                                                                                                      |                                                                                                                                        |  |  |

| 3-4-3, Kasumigaseki, Chiyoda-ku,     |                                                                                                      |                                                                                                                                        |  |  |

| Tokyo 100-8915, Japan                |                                                                                                      | Telephone No.                                                                                                                          |  |  |

### INTERNATIONAL SEARCH REPORT

International application No.

PCT/JP2019/023188

| C (Continuation | ). DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                       |                       |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Category*       | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                           | Relevant to claim No. |

| Y<br>A          | JP 2012-243871 A (ADVANCED POWER DEVICE RESEARCH ASSOCIATION) 10 December 2012, paragraphs [0041]-[0049], fig. 11-12, 15 & US 2013/0307023 A1, paragraphs [0075]-[0083], fig. 11-12, 15 & EP 2662882 A1 & CN 103403840 A & WO 2012/157228 A1 | 3-4, 8<br>5-7         |

| A               | JP 2001-196575 A (MATSUSHITA ELECTRIC INDUSTRIAL CO., LTD.) 19 July 2001, paragraphs [0017]-[0028], fig. 1 & US 2001/0020700 A1, paragraphs [0038]-[0051], fig. 1                                                                            | 1-8                   |

| A               | WO 2008/062800 Al (PANASONIC CORP.) 29 May 2008, paragraphs [0064]-[0081], fig. 1-3 & US 2010/0097105 Al, paragraphs [0166]-[0183], fig. 1-3 & EP 2084750 Al & CN 101523614 A & JP 2013-191868 A                                             | 1-8                   |

|                 |                                                                                                                                                                                                                                              |                       |

#### Α. 発明の属する分野の分類(国際特許分類(IPC))

Int.Cl. H01L21/338(2006.01)i, C30B29/38(2006.01)i, H01L21/337(2006.01)i, H01L21/365(2006.01)i, H01L29/778 (2006. 01) i, H01L29/808 (2006. 01) i, H01L29/812 (2006. 01) i

### 調査を行った分野

調査を行った最小限資料(国際特許分類(IPC))

Int.Cl. H01L21/338, C30B29/38, H01L21/337, H01L21/365, H01L29/778, H01L29/808, H01L29/812

#### 最小限資料以外の資料で調査を行った分野に含まれるもの

日本国実用新案公報 1922-1996年 1971-2019年 日本国公開実用新案公報 日本国実用新案登録公報 1996-2019年 日本国登録実用新案公報 1994-2019年

国際調査で使用した電子データベース(データベースの名称、調査に使用した用語)

#### 関連すると認められる文献

| し. 異連りると記めりはる文献         |                                                               |                |  |

|-------------------------|---------------------------------------------------------------|----------------|--|

| 引用文献の<br>カテゴリー <b>*</b> | 引用文献名 及び一部の箇所が関連するときは、その関連する箇所の表示                             | 関連する<br>請求項の番号 |  |

|                         |                                                               |                |  |

| Y                       | JP 2015-115582 A (ルネサスエレクトロニクス株式会社)                           | 1-4, 8         |  |

| A                       | 2015.06.22,段落[0017]-[0120],図 1-3 & US 2015/0171204 A1,段落      | 5-7            |  |

|                         | [0058]-[0161],図 1-3 & EP 2884539 A1 & CN 104716176 A & KR     |                |  |

|                         | 10-2015-0070001 A & TW 201528503 A                            |                |  |

| Y                       | <br>  JP 2017-521869 A(トランスフォーム インコーポレーテッド)                   | 1-4, 8         |  |

| Α                       | 2017.08.03,段落[0004],[0088]-[0092],[0106]-[0115],図             | 5-7            |  |

|                         | 1,10,14F & US 2016/0020313 A1,段落[0005],[0104]-[0108],         |                |  |

|                         | [0123]-[0131],図 1,10,14F & WO 2016/014439 A1 & CN 106537560 A |                |  |

### で欄の続きにも文献が列挙されている。

パテントファミリーに関する別紙を参照。

#### \* 引用文献のカテゴリー

- 「A」特に関連のある文献ではなく、一般的技術水準を示す 「T」国際出願日又は優先日後に公表された文献であって もの

- 「E」国際出願日前の出願または特許であるが、国際出願日 以後に公表されたもの

- 「L」優先権主張に疑義を提起する文献又は他の文献の発行 日若しくは他の特別な理由を確立するために引用す る文献(理由を付す)

- 「O」口頭による開示、使用、展示等に言及する文献

- 「P」国際出願日前で、かつ優先権の主張の基礎となる出願 「&」同一パテントファミリー文献

#### の日の後に公表された文献

- 出願と矛盾するものではなく、発明の原理又は理論 の理解のために引用するもの

- 「X」特に関連のある文献であって、当該文献のみで発明 の新規性又は進歩性がないと考えられるもの

- 「Y」特に関連のある文献であって、当該文献と他の1以 上の文献との、当業者にとって自明である組合せに よって進歩性がないと考えられるもの

| 国際調査を完了した日 07.08.2019                               | 国際調査報告の発送日<br>20.08.               | 201 | 1 9  |

|-----------------------------------------------------|------------------------------------|-----|------|

| 国際調査機関の名称及びあて先                                      | 特許庁審査官(権限のある職員)                    | 5 F | 6311 |

| 日本国特許庁(ISA/JP)<br>郵便番号100-8915<br>東京都千代田区霞が関三丁目4番3号 | 杉山 芳弘<br>電話番号 03-3581-1101 内線 3516 |     |      |

| C(続き).                  | 関連すると認められる文献                                                                                                                                                                             |                |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 引用文献の<br>カテゴリー <b>*</b> | 引用文献名 及び一部の箇所が関連するときは、その関連する箇所の表示                                                                                                                                                        | 関連する<br>請求項の番号 |

| Y<br>A                  | JP 2012-243871 A (次世代パワーデバイス技術研究組合)<br>2012.12.10, 段落[0041]-[0049],図 11-12,15<br>& US 2013/0307023 A1,段落[0075]-[0083],図 11-12,15<br>& EP 2662882 A1 & CN 103403840 A & WO 2012/157228 A1 | 3-4, 8<br>5-7  |

| A                       | JP 2001-196575 A (松下電器産業株式会社)<br>2001.07.19, 段落[0017]-[0028],図1<br>& US 2001/0020700 A1,段落[0038]-[0051],図1                                                                               | 1-8            |

| A                       | WO 2008/062800 A1 (パナソニック株式会社) 2008.05.29, 段落[0064]-[0081],図 1-3 & US 2010/0097105 A1, 段落[0166]-[0183],図 1-3 & EP 2084750 A1 & CN 101523614 A & JP 2013-191868 A                         | 1-8            |