(19) 世界知的所有権機関 国際事務局

(43) 国際公開日 2020年1月2日(02.01,2020)

(10) 国際公開番号

# WO 2020/003436 A1

(51) 国際特許分類:

**H01L 21/338** (2006.01) **H01L 29/812** (2006.01) **H01L 29/778** (2006.01)

(21) 国際出願番号: PCT/JP2018/024584

(22) 国際出願日: 2018年6月28日(28.06.2018)

(25) 国際出願の言語: 日本語

(26) 国際公開の言語: 日本語

- (71) 出願人:三菱電機株式会社(MITSUBISHI ELECTRIC CORPORATION) [JP/JP]; 〒1008310 東京都千代田区丸の内二丁目7番3号 Tokyo (JP).

- (72) 発明者: 吉 嗣 晃 治 (YOSHITSUGU Koji); 〒1008310 東京都千代田区丸の内二丁目7番 3号 三菱電機株式会社内 Tokyo (JP). 仲村 恵右(NAKAMURA Keisuke); 〒1008310 東京都 千代田区丸の内二丁目7番3号 三菱電機株 式会社内 Tokyo (JP). 柳生 栄治(YAGYU Eiji);

〒1008310 東京都千代田区丸の内二丁目7番 3号三菱電機株式会社内 Tokyo (JP).

- (74) 代理人: 吉竹 英俊, 外(YOSHITAKE Hidetoshi et al.); 〒5400001 大阪府大阪市中央区城見 1 丁目 4 番 7 0 号住友生命 O B P プラザビル 1 0階 Osaka (JP).

- (81) 指定国(表示のない限り、全ての種類の国内保護が可能): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DJ, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JO, JP, KE, KG, KH, KN, KP, KR, KW, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(54) Title: SEMICONDUCTOR DEVICE, AND MANUFACTURING METHOD FOR SEMICONDUCTOR DEVICE

(54) 発明の名称: 半導体装置、および、半導体装置の製造方法

(57) **Abstract:** The technology indicated in the present specification relates to a semiconductor device and a manufacturing method therefor, and a purpose thereof is to provide a semiconductor device that has a high heat dissipation ability. A semiconductor device according to the technology indicated in the present specification comprises a diamond substrate (23) and nitride semiconductor layers (2, 3). The diamond substrate (23) comprises diamond. The nitride semiconductor layers (2, 3) are formed in the interiors of recesses (17) that are formed in an upper surface (109) of the diamond substrate (23).

(57) 要約:本願明細書に開示される技術は、半導体装置およびその製造方法に関するものであり、かつ、高い放熱性能を有する半導体装置を提供することを目的とするものである。本願明細書に開示される技術に関する半導体装置は、ダイヤモンド基板(23)と、窒化物半導体層(2、3)とを備えるものである。ダイヤモンド基板(23)は、ダイヤモンドからなる。窒化物半導体層(2、3)は、ダイヤモンド基板(23)の上面(109)に形成された凹部(17)の内部に形成される。

(84) 指定国(表示のない限り、全ての種類の広域保護が可能): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), ユーラシア (AM, AZ, BY, KG, KZ, RU, TJ, TM), ヨーロッパ (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

#### 添付公開書類:

一 国際調査報告(条約第21条(3))

# 明 細 書

# 発明の名称 : 半導体装置、および、半導体装置の製造方法 技術分野

[0001] 本願明細書に開示される技術は、半導体装置およびその製造方法に関するものである。

# 背景技術

- [0002] 従来から、高出力、かつ、高周波領域で動作する半導体装置として、窒化物系半導体から作製される電界効果型トランジスタなどが用いられている。 しかしながら、高出力動作中に半導体装置内部の温度が上昇することによって、装置の特性または信頼性が低下する現象が問題となっている。

- [0003] この半導体装置内部の温度上昇を抑制するためには、放熱性が高い材料または放熱性が高い構造を発熱部近傍に設けることが重要である。ダイヤモンドは、固体物質中で最も高い熱伝導率を誇っており、放熱用材料として最適である。

- [0004] 従来のダイヤモンド基板を用いる半導体装置では、半導体装置の基板の一部に設けられたバイア内に、ダイヤモンドが少なくとも部分的に充填される。そうすることによって、半導体装置内で生じた熱を厚さ方向に逃がすことができる(たとえば、特許文献 1 を参照)。

- [0005] 一方、より高い放熱効果が見込まれる半導体装置では、半導体装置の基板 全体をダイヤモンドで置換することによって、半導体装置内で生じた熱を放 散状に効率よく逃がすことができる(たとえば、非特許文献1を参照)。

#### 先行技術文献

# 特許文献

[0006] 特許文献1:特許第6174113号公報

# 非特許文献

[0007] 非特許文献1:G. H. Jessen et al., "AlGaN/ GaN HEMT on Diamond Technology Dem onstration", in Proceedings of CSICS, IEEE, TX, pp. 271-274 (2006).

# 発明の概要

# 発明が解決しようとする課題

- [0008] 放熱効果を最大化するためには、発熱源近傍に熱伝導率の高い放熱用材料 を配置して、熱を効率よく逃がすことが求められる。

- [0009] しかしながら、従来技術では、放熱用材料であるダイヤモンドが、基板の 一部のバイア内部、または、基板にのみ適用されており、また、主たる放熱 方向は膜厚方向に制限されていた。

- [0010] 放熱が膜厚方向に制限されている場合、半導体装置の活性領域で生じる温度上昇は、十分に低減することができない恐れがある。

- [0011] 本願明細書に開示される技術は、以上に記載されたような問題を解決する ためになされたものであり、高い放熱性能を有する半導体装置を提供するこ とを目的とするものである。

#### 課題を解決するための手段

- [0012] 本願明細書に開示される技術の第1の態様は、ダイヤモンドからなるダイヤモンド基板と、前記ダイヤモンド基板の上面に形成された凹部の内部に形成される窒化物半導体層とを備える。

- [0013] 本願明細書に開示される技術の第2の態様は、半導体基板の上面に窒化物 半導体層を形成し、前記窒化物半導体層の表面と支持基板とを接合し、前記 半導体基板の下面にハードマスクを形成し、前記ハードマスクに開口領域を 有するパターンを形成し、前記開口領域に対応する前記半導体基板、さらに は、前記窒化物半導体層を除去することによって、前記半導体基板および前 記窒化物半導体層を貫通する溝を形成し、前記ハードマスクおよび前記半導 体基板を除去し、前記支持基板の表面に、前記窒化物半導体層を覆うダイヤ モンド層を形成し、前記窒化物半導体層の表面および前記ダイヤモンド層の 表面と、前記支持基板とを遊離させる。

- [0014] 本願明細書に開示される技術の第3の態様は、ダイヤモンドからなるダイ

ヤモンド基板を用意し、前記ダイヤモンド基板の表面にハードマスクを形成 し、前記ハードマスクに開口領域を有するパターンを形成し、前記開口領域 に対応する前記ダイヤモンド基板を除去することによって凹部を形成し、前 記凹部の内部に窒化物半導体層をエピタキシャル成長させる。

#### 発明の効果

- [0015] 本願明細書に開示される技術の第1の態様は、ダイヤモンドからなるダイヤモンド基板と、前記ダイヤモンド基板の上面に形成された凹部の内部に形成される窒化物半導体層とを備えるものである。このような構成によれば、高い熱伝導率を有するダイヤモンドが、窒化物半導体層の下面に加えて側面にも接触して形成されている。そのため、窒化物半導体層の上面に素子構造などが形成されることによって窒化物半導体層を含む半導体装置が発熱源となる場合、半導体装置の下方に加えて側方に高い放熱性能を発揮することができる。したがって、半導体装置の温度上昇を大幅に抑制することができる

- [0016] 本願明細書に開示される技術の第2の態様は、半導体基板の上面に窒化物半導体層を形成し、前記窒化物半導体層の表面と支持基板とを接合し、前記半導体基板の下面にハードマスクを形成し、前記ハードマスクに開口領域を有するパターンを形成し、前記開口領域に対応する前記半導体基板、さらには、前記窒化物半導体層を除去することによって、前記半導体基板および前記窒化物半導体層を貫通する溝を形成し、前記ハードマスクおよび前記半導体基板を除去し、前記支持基板の表面に、前記窒化物半導体層を覆うダイヤモンド層を形成し、前記窒化物半導体層の表面および前記ダイヤモンド層の表面と、前記支持基板とを遊離させる。このような構成によれば、半導体基板を全面的に除去する工程の前に、半導体基板および窒化物半導体層を貫通する溝をあらかじめ形成しておくことによって、窒化物半導体層において、応力緩和に起因するクラックまたは割れが生じることを抑制することができる。

- [0017] 本願明細書に開示される技術の第3の態様は、ダイヤモンドからなるダイ

ヤモンド基板を用意し、前記ダイヤモンド基板の表面にハードマスクを形成し、前記ハードマスクに開口領域を有するパターンを形成し、前記開口領域に対応する前記ダイヤモンド基板を除去することによって凹部を形成し、前記凹部の内部に窒化物半導体層をエピタキシャル成長させる。このような構成によれば、半導体装置の製造を簡便に行うことができる。

[0018] 本願明細書に開示される技術に関する目的と、特徴と、局面と、利点とは 、以下に示される詳細な説明と添付図面とによって、さらに明白となる。

# 図面の簡単な説明

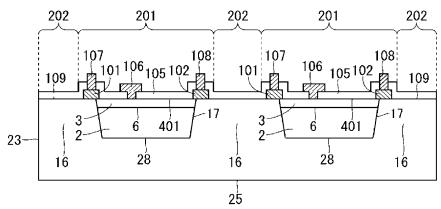

[0019] [図1]実施の形態に関する、半導体装置の構成の例を概略的に示す断面図である。

[図2]実施の形態に関する、半導体装置の構成の例を概略的に示す断面図である。

[図3]実施の形態に関する、半導体装置の構成の別の例を概略的に示す断面図である。

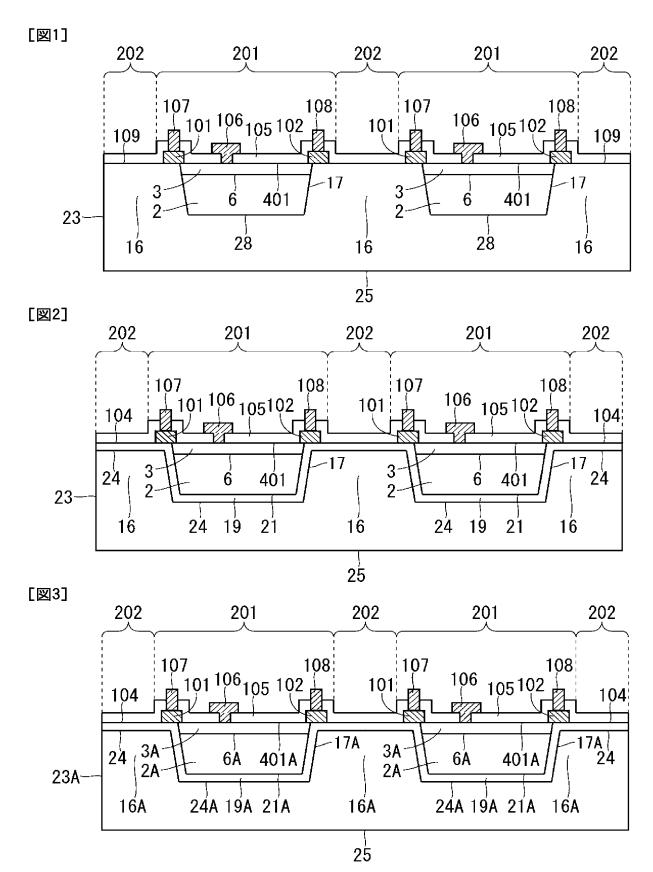

[図4]実施の形態に関する、半導体装置の構成の例を概略的に示す断面図である。

[図5]実施の形態に関する、半導体装置の構成の例を概略的に示す断面図である。

[図6]実施の形態に関する、半導体装置の構成の別の例を概略的に示す断面図である。

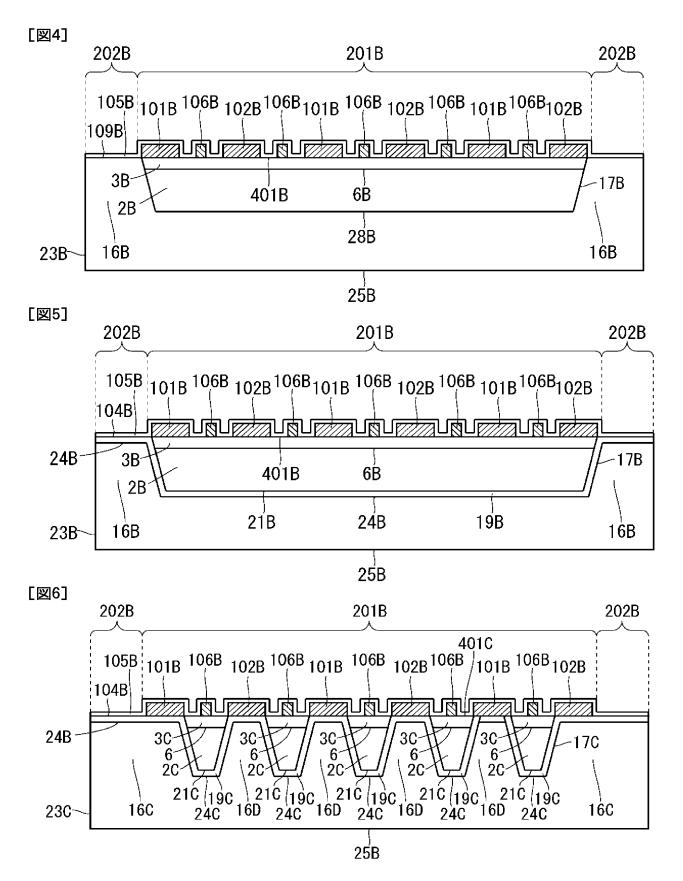

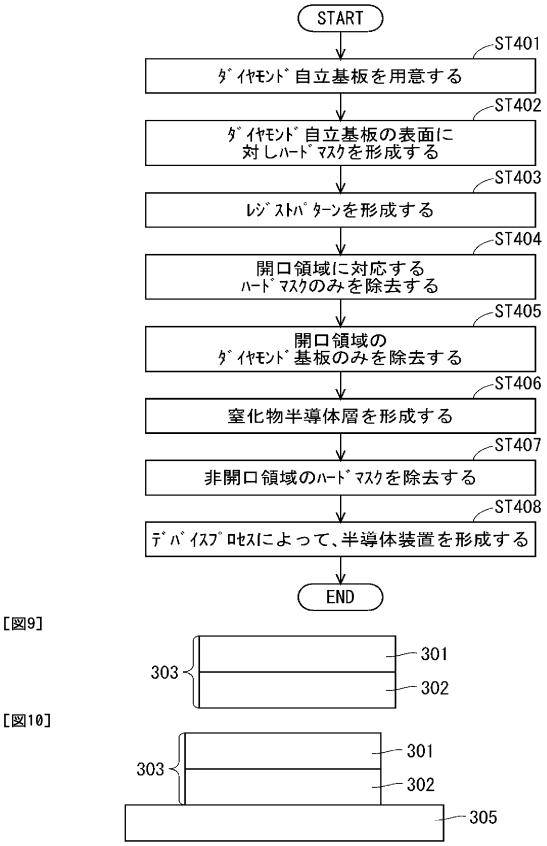

[図7]実施の形態における半導体装置の、製造方法の例を示すフローチャートである。

[図8]図1から図6に例が示された半導体装置の、製造方法の別の例を示すフローチャートである。

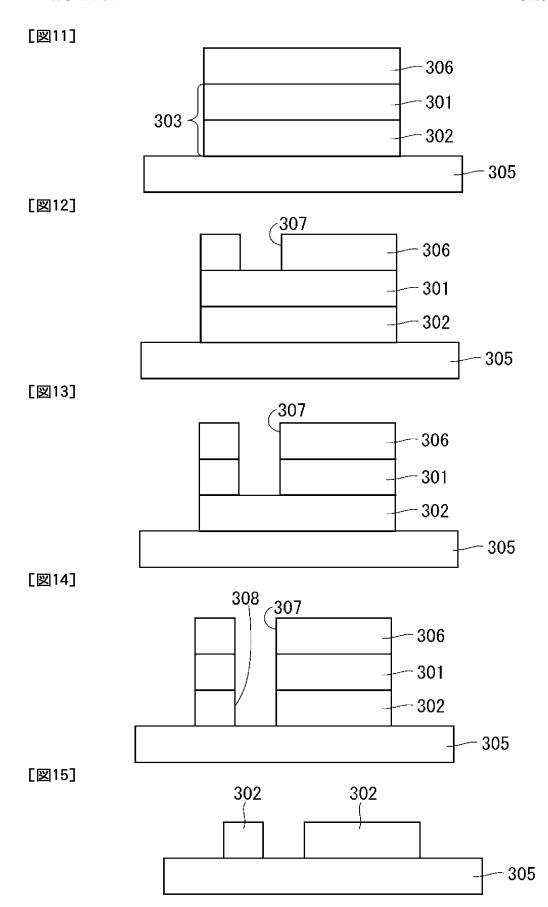

[図9]実施の形態に関する半導体装置の、製造工程の例を示す断面図である。 [図10]実施の形態に関する半導体装置の、製造工程の例を示す断面図である

[図11]実施の形態に関する半導体装置の、製造工程の例を示す断面図である

0

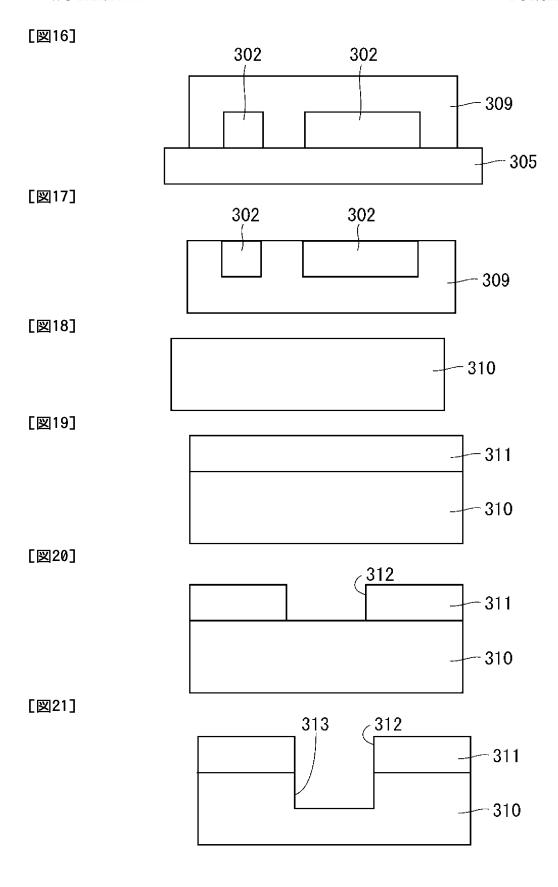

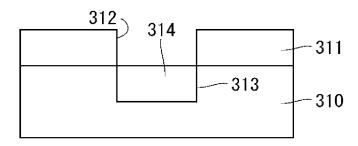

[図12]実施の形態に関する半導体装置の、製造工程の例を示す断面図である [図13]実施の形態に関する半導体装置の、製造工程の例を示す断面図である [図14]実施の形態に関する半導体装置の、製造工程の例を示す断面図である [図15]実施の形態に関する半導体装置の、製造工程の例を示す断面図である [図16]実施の形態に関する半導体装置の、製造工程の例を示す断面図である [図17]実施の形態に関する半導体装置の、製造工程の例を示す断面図である [図18]実施の形態に関する半導体装置の、製造工程の例を示す断面図である [図19]実施の形態に関する半導体装置の、製造工程の例を示す断面図である [図20]実施の形態に関する半導体装置の、製造工程の例を示す断面図である [図21]実施の形態に関する半導体装置の、製造工程の例を示す断面図である [図22]実施の形態に関する半導体装置の、製造工程の例を示す断面図である [図23]実施の形態に関する半導体装置の、製造工程の例を示す断面図である

# 発明を実施するための形態

[0020] 以下、添付される図面を参照しながら実施の形態について説明する。

[0021] なお、図面は概略的に示されるものであり、説明の便宜のため、適宜、構

成の省略、または、構成の簡略化がなされるものである。また、異なる図面にそれぞれ示される構成などの大きさおよび位置の相互関係は、必ずしも正確に記載されるものではなく、適宜変更され得るものである。また、断面図ではない平面図などの図面においても、実施の形態の内容を理解することを容易にするために、ハッチングが付される場合がある。

- [0022] また、以下に示される説明では、同様の構成要素には同じ符号を付して図示し、それらの名称と機能とについても同様のものとする。したがって、それらについての詳細な説明を、重複を避けるために省略する場合がある。

- [0023] また、以下に記載される説明において、「上」、「下」、「左」、「右」、「側」、「底」、「表」または「裏」などの特定の位置と方向とを意味する用語が用いられる場合があっても、これらの用語は、実施の形態の内容を理解することを容易にするために便宜上用いられるものであり、実際に実施される際の方向とは関係しないものである。

- [0024] <第1の実施の形態>

以下、本実施の形態に関する半導体装置、および、半導体装置の製造方法について説明する。

[0025] <半導体装置の構成について>

図1は、本実施の形態に関する半導体装置の構成の例を概略的に示す断面図である。図1に例が示されるように、半導体装置は、ダイヤモンドからなるダイヤモンド基板23の凹部17の内部に形成される窒化物半導体層であるエピタキシャル半導体層2と、エピタキシャル半導体層2の上面に形成されるエピタキシャル半導体層3と、エピタキシャル半導体層3の上面401に部分的に形成されるソースまたはドレイン電極金属101と、エピタキシャル半導体層3の上面401に部分的に形成されるドレインまたはソース電極金属102と、エピタキシャル半導体層3の上面401に部分的に形成されるゲート電極金属106と、凸部16の上面109およびエピタキシャル半導体層3の上面401を部分的に覆って形成される表面保護膜105と、ソースまたはドレイン電極金属101の上面を部

分的に覆って形成されるソースまたはドレインパッド電極金属107と、ドレインまたはソース電極金属102の上面を部分的に覆って形成されるドレインまたはソースパッド電極金属108とを備える。

- [0026] ダイヤモンド基板23は、上面109と下面25とを有する。ダイヤモンド基板23の上面109には凸部16が形成され、平面視において凸部16に四方を囲まれた凹部17には、GaNまたはAIN系の材料(以下、窒化物系半導体材料とする)のエピタキシャル半導体層2とエピタキシャル半導体層3が充填されている。ここで、凹部17は、平面視において凸部16に囲まれていない場合であってもよい。すなわち、たとえば、凹部17が紙面表裏方向に延びるストライプ構造であってもよい(以下の実施の形態において同様)。

- [0027] エピタキシャル半導体層 2 およびエピタキシャル半導体層 3 の材料は、たとえば、S i、G a A s、S i C またはG a  ${}_2$  O  ${}_3$  などを含む。

- [0028] また、本実施の形態では、エピタキシャル半導体層2とエピタキシャル半導体層3とが積層されているが、単一のエピタキシャル半導体層が凹部17 に形成されていてもよい。

- [0029] エピタキシャル半導体層3の上面401には、電界効果トランジスタ20 1が形成される。ここで、電界効果トランジスタとは、たとえば、金属一絶 縁体一半導体(metal-insulator-semiconduct or、すなわち、MIS)型電界効果トランジスタ、金属一酸化物一半導体 (metal-oxide-semiconductor、すなわち、MO S)型電界効果トランジスタ、または、高電子移動度トランジスタ(hig h electron mobility transistor、すなわ ち、HEMT)などの横型半導体装置を指す。本実施の形態では、HEMT デバイスを例として示す。

- [0030] なお、エピタキシャル半導体層3の上面401は、ダイヤモンド基板23 の上面109と同一平面上に位置する。

- [0031] エピタキシャル半導体層3の上面401に形成されるHEMTデバイスは

- 、ソースまたはドレイン電極金属101と、ドレインまたはソース電極金属102と、ゲート電極金属106とを備える。

- [0032] また、エピタキシャル半導体層3の上面401に形成されるHEMTデバイスは、ソースまたはドレインパッド電極金属107と、ドレインまたはソースパッド電極金属108とを備えていてもよい。

- [0033] ゲート電極金属106の形状は、本実施の形態において目的に適合するいかなる形状であってもよい。また、ゲート電極金属106の上面には、フィールドプレート電極金属が形成されていてもよい。

- [0034] 電極が形成されていない領域におけるエピタキシャル半導体層3の上面4 01には、少なくとも1層の表面保護膜105が形成される。表面保護膜1 05は、電界の制御または表面ポテンシャルの制御、さらには、表面準位の 不活性化、耐水、または、耐湿などの機能を担っている。ゲート電極金属1 06の一部は、表面保護膜105の一部を覆って形成されていなくてもよい

- [0035] そして、隣り合う電界効果トランジスタ201の間隙には、素子間分離領域202が存在する。素子間分離領域202は、ダイヤモンド基板の上面1 09の凸部16に形成される。

- [0036] このような半導体装置の構成によれば、平面視において、電界効果トランジスタ201の四方を高熱伝導率材料であるダイヤモンド基板23が取り囲むことになる。

- [0037] 熱は、電界効果トランジスタ201の活性領域で発生する。そのため、平面視における活性領域の四方を高熱伝導率材料が取り囲むことによって、本実施の形態に関する半導体装置は高い放熱効率を発揮する。また、エピタキシャル半導体層2とダイヤモンド基板23とは直接接触して接合界面28を形成しているため、界面熱抵抗の影響が少ない。よって、シームレスに(すなわち、継ぎ目がない状態で)熱を逃がすことができる。

- [0038] また、ダイヤモンドは、一般に電気絶縁性が高い材料である。そのため、 本実施の形態において適用されるダイヤモンド基板23の電気抵抗率が、少

なくともエピタキシャル半導体層2の電気抵抗率またはエピタキシャル半導体層3の電気抵抗率よりも十分に高い場合、ダイヤモンド基板23の凸部16は、素子間分離の機能を発揮することができる。

- [0039] HEMTデバイスの作製工程においては、通常、素子間分離工程が必要であり、ドライエッチングプロセスによってキャリアとなる2次元電子ガスを物理的に消失させる手法、または、選択イオン注入プロセスによって素子分離領域に相当する領域のエピタキシャル半導体結晶を物理的に破壊する手法などが採用されている。

- [0040] 一方で、図1に例が示された半導体装置の構成においては、結晶ダイヤモンドが電気絶縁性を有するため、前述の煩雑な素子間分離工程を簡略化することができる。

- [0041] <第2の実施の形態>

本実施の形態に関する半導体装置、および、半導体装置の製造方法について説明する。以下の説明においては、以上に記載された実施の形態で説明された構成要素と同様の構成要素については同じ符号を付して図示し、その詳細な説明については適宜省略するものとする。

[0042] <半導体装置の構成について>

図1においては、エピタキシャル半導体層2とダイヤモンド基板23とが 直接接触していたが、本実施の形態では、エピタキシャル半導体層2とダイ ヤモンド基板23とが直接接触していない構成について説明する。

[0043] 図2は、本実施の形態に関する半導体装置の構成の例を概略的に示す断面図である。図2に例が示されるように、半導体装置は、ダイヤモンド基板23と、ダイヤモンド基板23の凸部16および凹部17の内壁を覆って形成される密着層または核形成層19と、密着層または核形成層19に覆われたダイヤモンド基板23の凹部17に形成されるエピタキシャル半導体層2と、エピタキシャル半導体層3と、ソースまたはドレイン電極金属101と、ドレインまたはソース電極金属102と、ゲート電極金属106と、表面保護膜105と、ソースまたはドレインパッド電極金属107と、ドレインま

たはソースパッド電極金属108とを備える。

- [0044] ダイヤモンド基板23は、密着層または核形成層19と直接接触することによって接合界面24を形成する。また、エピタキシャル半導体層2は、密着層または核形成層19と直接接触することによって、接合界面21を形成する。

- [0045] 密着層または核形成層 1 9 の材料としては、たとえば、非晶質 S i または 窒化 S i などの非晶質材料が一般的に用いられる。しかしながら、密着層ま たは核形成層 1 9 の材料として、結晶系材料が用いられてもよい。

- [0046] ダイヤモンド基板23の凹部17に、エピタキシャル半導体層2を成長させる場合、密着層または核形成層19の材料として、ダイヤモンドシードと呼ばれるダイヤモンドナノ粒子が用いられてもよい。なお、放熱効率の観点から、密着層または核形成層19の厚さは、たとえば、50nm以下であることが望ましい。

- [0047] このような半導体装置の構成によれば、密着層または核形成層 1 9 がダイヤモンド基板 2 3 とエピタキシャル半導体層 2 との間に介在することによって、ダイヤモンド基板 2 3 とエピタキシャル半導体層 2 との間において膜剥がれ、欠損、または、クラックなどが混入することを抑制することができる。そのため、異種材料間の接合の密着性を向上させることができる。

#### [0048] <第3の実施の形態>

本実施の形態に関する半導体装置、および、半導体装置の製造方法について説明する。以下の説明においては、以上に記載された実施の形態で説明された構成要素と同様の構成要素については同じ符号を付して図示し、その詳細な説明については適宜省略するものとする。

[0049] <半導体装置の構成について>

図3は、本実施の形態に関する半導体装置の構成の別の例を概略的に示す断面図である。図3に例が示される構成は、図1および図2に例が示された構成とは異なり、凸部16Aの位置が素子間分離領域202には対応していない。つまり、図3に例が示される構成は、ダイヤモンド基板23Aの凹部

17Aの幅が狭い、すなわち、ダイヤモンド基板23Aの凸部16Aの幅が 広い。そして、凸部16Aは、凸部16Aに隣接するソースまたはドレイン 電極金属101の直下、および、ドレインまたはソース電極金属102の直 下にまで延びて形成される。

- [0050] 図3に例が示されるように、半導体装置は、ダイヤモンド基板23Aと、ダイヤモンド基板23Aの凸部16Aおよび凹部17Aを覆って形成される密着層または核形成層19Aに覆われたダイヤモンド基板23Aの凹部17Aに形成されるエピタキシャル半導体層2Aと、エピタキシャル半導体層2Aの上面に形成されるエピタキシャル半導体層3Aと、密着層または核形成層19Aに覆われた凸部16Aの上面に部分的に形成されるソースまたはドレイン電極金属101と、密着層または核形成層19Aに覆われた凸部16Aの上面に部分的に形成されるソースまたはドレイン電極金属101と、密着層または核形成層19Aに覆われた凸部16Aの上面に部分的に形成されるドレインまたはソース電極金属102と、エピタキシャル半導体層3Aの上面401Aに部分的に形成されるゲート電極金属106と、凸部16Aの上面およびエピタキシャル半導体層3Aの上面401Aに部分的に形成される表面保護膜105と、ソースまたはドレインパッド電極金属107と、ドレインまたはソースパッド電極金属108とを備える。なお、図3において、密着層または核形成層19Aは形成されていなくてもよい。

- [0051] ダイヤモンド基板23Aは、密着層または核形成層19Aと直接接触することによって接合界面24Aを形成する。また、エピタキシャル半導体層2Aは、密着層または核形成層19Aと直接接触することによって、接合界面21Aを形成する。

- [0052] このような半導体装置の構成によれば、より近い距離で、平面視における 電界効果トランジスタ201の四方を高熱伝導率材料であるダイヤモンド基 板23Aが取り囲むことになる。

- [0053] 熱は、電界効果トランジスタ201の活性領域で発生する。そのため、平面視における活性領域の四方を高熱伝導率材料が取り囲むことによって、本実施の形態に関する半導体装置は高い放熱効率を発揮する。

## [0054] <第4の実施の形態>

本実施の形態に関する半導体装置、および、半導体装置の製造方法について説明する。以下の説明においては、以上に記載された実施の形態で説明された構成要素と同様の構成要素については同じ符号を付して図示し、その詳細な説明については適宜省略するものとする。

[0055] <半導体装置の構成について>

マイクロ波通信システム、または、ミリ波通信システムなどに用いられるマイクロ波モノリシック集積回路(monolithic microwave integrated circuit、すなわち、MMIC)は、HEMTデバイスによって構成されている。

- [0056] MMICの高出力電力増幅器に利用されるHEMTデバイスには、複数の単位HEMTを電気的に並列接続するマルチフィンガー型HEMTが採用されている。

- [0057] マルチフィンガー型HEMTでは、互いに並列接続されたそれぞれの単位 HEMTの発熱は、無視することができない量となる。特に、マルチフィン ガー型HEMTの中心付近に位置する単位HEMTデバイスは、その周囲に 位置する単位HEMTデバイスからの発熱の影響を受けて熱が集中するため 、放熱効率が悪くなる。その結果、マルチフィンガー型HEMTの中心付近 に位置する単位HEMTデバイスは、破壊されやすくなる。

- [0058] したがって、高出力電力増幅器におけるマルチフィンガー型HEMTの性能を向上させるためには、放熱効率の高い構造を採用する必要がある。

- [0059] 図4は、本実施の形態に関する半導体装置の構成の例を概略的に示す断面 図である。図4に例が示される半導体装置は、複数の電界効果トランジスタ が電気的に並列接続されたマルチフィンガー型電界効果トランジスタである

- [0060] ここで、並列接続される単位電界効果トランジスタは、たとえば、MIS型、MOS型、または、HEMTデバイスであってもよい。ここでは、マルチフィンガー型HEMTを例として示す。

- [0061] 図4に例が示されるように、半導体装置は、ダイヤモンド基板23Bと、ダイヤモンド基板23Bの凹部17Bに形成されるエピタキシャル半導体層2Bと、エピタキシャル半導体層2Bの上面に形成されるエピタキシャル半導体層3Bと、エピタキシャル半導体層3Bの上面401Bに部分的に形成されるソースまたはドレイン電極金属101Bと、エピタキシャル半導体層3Bの上面401Bに部分的に形成されるドレインまたはソース電極金属102Bと、エピタキシャル半導体層3Bの上面401Bに部分的に形成されるゲート電極金属106Bと、エピタキシャル半導体層3Bの上面401B、および、凸部16Bの上面109Bを覆って形成される表面保護膜105Bとを備える。

- [0062] ダイヤモンド基板23Bは、上面109Bと下面25Bとを有する。ダイヤモンド基板23Bの上面109Bには凸部16Bが形成され、平面視において凸部16Bに四方を囲まれた凹部17Bには、エピタキシャル半導体層2Bとエピタキシャル半導体層3Bが充填されている。

- [0063] エピタキシャル半導体層 2 B およびエピタキシャル半導体層 3 B の材料は、たとえば、Si、GaAs、SiCまたは $Ga_2O_3$ などを含む。

- [0064] また、本実施の形態では、エピタキシャル半導体層2Bとエピタキシャル半導体層3Bとが積層されているが、単一のエピタキシャル半導体層が凹部 17Bに形成されていてもよい。

- [0065] エピタキシャル半導体層3Bの上面401Bには、マルチフィンガー型HEMT201Bが形成される。エピタキシャル半導体層3Bの上面401Bに形成されるマルチフィンガー型HEMT201Bでは、ソースまたはドレイン電極金属101Bと、ドレインまたはソース電極金属102Bと、ゲート電極金属106Bとを備える単位HEMTが、ドレイン配線、ゲート配線およびソース配線によって電気的に並列に接続されている。

- [0066] ゲート電極金属106Bの形状は、本実施の形態において目的に適合するいかなる形状であってもよい。また、ゲート電極金属106Bの上面には、フィールドプレート電極金属が形成されていてもよい。

- [0067] また、マルチフィンガー型HEMT201Bにおいて、単位HEMTデバイスはいくつ並列に接続されていてもよい。

- [0068] 電極が形成されていない領域におけるエピタキシャル半導体層3Bの上面401B、および、それぞれの電極上には、少なくとも1層の表面保護膜105Bが形成される。表面保護膜105Bは、電界の制御または表面ポテンシャルの制御、さらには、表面準位の不活性化、耐水、または、耐湿などの機能を担っている。

- [0069] そして、隣り合うマルチフィンガー型HEMT201Bの間隙には、素子間分離領域202Bが存在する。素子間分離領域202Bは、ダイヤモンド基板の上面109Bの凸部16Bに形成される。

- [0070] このような半導体装置の構成によれば、平面視において、マルチフィンガー型HEMT201Bの四方を高熱伝導率材料であるダイヤモンド基板23 Bが取り囲むことになる。

- [0071] 熱は、マルチフィンガー型HEMT201Bの活性領域で発生する。そのため、平面視における活性領域の四方を高熱伝導率材料が取り囲むことによって、本実施の形態に関する半導体装置は高い放熱効率を発揮する。また、エピタキシャル半導体層2Bとダイヤモンド基板23Bとは直接接触して接合界面28Bを形成しているため、界面熱抵抗の影響が少ない。よって、シームレスに(すなわち、継ぎ目がない状態で)熱を逃がすことができる。

- [0072] また、ダイヤモンドは、一般に電気絶縁性が高い材料である。そのため、本実施の形態において適用されるダイヤモンド基板23Bの電気抵抗率が、少なくともエピタキシャル半導体層2Bの電気抵抗率またはエピタキシャル半導体層3Bの電気抵抗率よりも十分に高い場合、ダイヤモンド基板23Bの凸部16Bは、素子間分離の機能を発揮することができる。

- [0073] HEMTデバイスの作製工程においては、通常、素子間分離工程が必要であり、ドライエッチングプロセスによってキャリアとなる2次元電子ガスを物理的に消失させる手法、または、選択イオン注入プロセスによって素子分離領域に相当する領域のエピタキシャル半導体結晶を物理的に破壊する手法

などが採用されている。

[0074] 一方で、図4に例が示された半導体装置の構成においては、結晶ダイヤモンドが電気絶縁性を有するため、前述の煩雑な素子間分離工程を簡略化することができる。

#### [0075] <第5の実施の形態>

本実施の形態に関する半導体装置、および、半導体装置の製造方法について説明する。以下の説明においては、以上に記載された実施の形態で説明された構成要素と同様の構成要素については同じ符号を付して図示し、その詳細な説明については適宜省略するものとする。

[0076] <半導体装置の構成について>

図4においては、エピタキシャル半導体層2Bとダイヤモンド基板23B とが直接接触していたが、本実施の形態では、エピタキシャル半導体層2B とダイヤモンド基板23Bとが直接接触していない構成について説明する。

- [0077] 図5は、本実施の形態に関する半導体装置の構成の例を概略的に示す断面図である。図5に例が示されるように、半導体装置は、ダイヤモンド基板23Bの凸部16Bおよび凹部17Bを覆って形成される密着層または核形成層19Bと、密着層または核形成層19Bに覆われたダイヤモンド基板23Bの凹部17Bに形成されるエピタキシャル半導体層2Bと、エピタキシャル半導体層3Bと、ソースまたはドレイン電極金属101Bと、ドレインまたはソース電極金属102Bと、ゲート電極金属106Bと、表面保護膜105Bとを備える。

- [0078] ダイヤモンド基板23Bは、密着層または核形成層19Bと直接接触することによって接合界面24Bを形成する。また、エピタキシャル半導体層2Bは、密着層または核形成層19Bと直接接触することによって、接合界面21Bを形成する。

- [0079] 密着層または核形成層 1 9 Bの材料としては、たとえば、非晶質 S i または窒化 S i などの非晶質材料が一般的に用いられる。しかしながら、密着層または核形成層 1 9 Bの材料として、結晶系材料が用いられてもよい。

[0080] ダイヤモンド基板23Bの凹部17Bに、エピタキシャル半導体層2Bを成長させる場合、密着層または核形成層19Bの材料として、ダイヤモンドナノ粒子が用いられてもよい。なお、放熱効率の観点から、密着層または核形成層19Bの厚さは、たとえば、50nm以下であることが望ましい。

[0081] このような半導体装置の構成によれば、密着層または核形成層 1 9 B が ダイヤモンド基板 2 3 B とエピタキシャル半導体層 2 B との間に介在することによって、ダイヤモンド基板 2 3 B とエピタキシャル半導体層 2 B との間において膜剥がれ、欠損、または、クラックなどが混入することを抑制することができる。そのため、異種材料間の接合の密着性を向上させることができる。

#### [0082] <第6の実施の形態>

本実施の形態に関する半導体装置、および、半導体装置の製造方法について説明する。以下の説明においては、以上に記載された実施の形態で説明された構成要素と同様の構成要素については同じ符号を付して図示し、その詳細な説明については適宜省略するものとする。

#### [0083] <半導体装置の構成について>

図6は、本実施の形態に関する半導体装置の構成の別の例を概略的に示す断面図である。図6に例が示される構成は、図4および図5に例が示された構成とは異なり、凸部16Cの位置が素子間分離領域202Bには対応していない。つまり、図6に例が示される構成は、ダイヤモンド基板23Cの凹部17Cの幅が狭く、かつ、隣り合う凸部16C間において複数形成されている。そして、凸部16Cは、凸部16Cに隣接するソースまたはドレイン電極金属101Bの直下、および、ドレインまたはソース電極金属102Bの直下にまで延びて形成される。

[0084] 図6に例が示されるように、半導体装置は、ダイヤモンド基板23Cと、 ダイヤモンド基板23Cの凸部16Cおよび凹部17Cを覆って形成される 密着層または核形成層19Cと、密着層または核形成層19Cに覆われたダ イヤモンド基板23Cの凹部17Cに形成されるエピタキシャル半導体層2 Cと、エピタキシャル半導体層2Cの上面に形成されるエピタキシャル半導体層3Cと、密着層または核形成層19Cに覆われた凸部16Cの上面に部分的に形成され、また、隣り合う凸部16C間に形成された複数の凹部17Cの間の凸部16Dの上面に形成されるソースまたはドレイン電極金属101Bと、密着層または核形成層19Cに覆われた凸部16Cの上面に部分的に形成され、また、複数の凹部17Cの間の凸部16Dの上面に形成されるドレインまたはソース電極金属102Bと、エピタキシャル半導体層3Cの上面401Cに部分的に形成されるゲート電極金属106Bと、エピタキシャル半導体層3Cの上面401Cに部分的に形成されるゲート電極金属106Bと、エピタキシャル半導体層3Cの上面401C、および、凸部16Cの上面を覆って形成される表面保護膜105Bとを備える。なお、図6において、密着層または核形成層19Cは形成されていなくてもよい。

- [0085] ダイヤモンド基板23Cは、密着層または核形成層19Cと直接接触することによって接合界面24Cを形成する。また、エピタキシャル半導体層2Cは、密着層または核形成層19Cと直接接触することによって、接合界面21Cを形成する。

- [0086] このような半導体装置の構成によれば、より近い距離で、平面視におけるマルチフィンガー型HEMT201Bの四方を高熱伝導率材料であるダイヤモンド基板23Cが取り囲むことになる。

- [0087] 熱は、マルチフィンガー型HEMT201Bの活性領域で発生し、特に、マルチフィンガー型HEMT201Bの中心部に集中する。そのため、平面視における活性領域の四方を高熱伝導率材料が取り囲むことによって、本実施の形態に関する半導体装置は高い放熱効率を発揮する。

- [0088] <第7の実施の形態>

本実施の形態に関する半導体装置、および、半導体装置の製造方法について説明する。以下の説明においては、以上に記載された実施の形態で説明された構成要素と同様の構成要素については同じ符号を付して図示し、その詳細な説明については適宜省略するものとする。

[0089] <半導体装置の構成について>

図7は、以上に記載された実施の形態における半導体装置の、製造方法の例を示すフローチャートである。また、図9から図17は、本実施の形態に関する半導体装置の、製造工程の例を示す断面図である。以下、図7および図9から図17を参照しつつ、本実施の形態に関する半導体装置の製造方法を説明する。

- [0090] まず、ステップST301において、製造加工のための出発基板として、 Si基板301の上面にGaN層302が形成されたGaN-on-Si基 板303を用意する(たとえば、図9を参照)。なお、本実施の形態に関する製造方法ではGaN-on-Si基板303が出発基板の例として挙げられているが、出発基板は、たとえば、GaN-on-サファイア基板または GaN-on-SiC基板などであってもよい。

- [0091] その後、ステップST302において、GaN-on-Si基板303の GaN層302の表面に対し、支持基板305を貼り付ける(たとえば、図 10を参照)。ここで、支持基板305には、たとえば、Si基板、サファ イア基板または石英基板などが用いられる。

- [0092] GaN表面の算術平均粗さ(Ra)は30nm以下となるように、事前に 平坦化加工が施されていることが望ましい。これは、支持基板305の貼付 面についても同様である。

- [0093] GaN-on-Si基板303のGaN層302の表面に対し支持基板305を貼り付ける方法としては、たとえば、親水化接合法、加圧接合法またはプラズマ活性化接合法などの接合法であってもよいし、無機系接着剤材料などを用いる接着法であってもよい。さらに、支持基板305とGaN-on-Si基板303のGaN層302の表面との貼り合わせ面に任意の層間膜が設けられてもよい。当該層間膜の材料としては、たとえば、窒化Siまたはアルミナ膜などの、半導体保護膜として一般に用いる材料であることが望ましい。

- [0094] このようにして、支持基板305とGaN層302の表面とが接合された 複合基板が作製することができる。

- [0095] その後、ステップST303において、支持基板305とGaN-on-Si基板303のGaN層302の表面とが接合された複合基板のうち、出発基板のSi基板301の表面に対しハードマスク306を形成する(たとえば、図11を参照)。

- [0096] ハードマスク306は、ドライエッチング耐性があり、かつ、Siまたは GaNに対しエッチングの選択比を有する材料であることが望ましい。ハードマスク306の材料は、たとえば、窒化Si、アルミナ膜または二酸化Siなどであってもよい。

- [0097] これらの材料の形成手法は、たとえば、スパッタ法または蒸着法などの物理気相堆積(physical vapor deposition、すなわち、PVD)法、または、減圧化学気相成長法、プラズマ援用化学気相成長法または原子層堆積法などの化学気相堆積(chemical vapor deposition、すなわち、CVD)法であってもよい。

- [0098] また、上記のハードマスク306は、ステップST304以降の貫通溝を 形成する工程におけるそれぞれの選択比に応じて、1層以上形成される構成 であってもよい。

- [0099] その後、ステップST304において、ステップST303において形成されたハードマスク306に対し、貫通溝を形成するためのレジストパターンを形成する。貫通溝のためのレジストパターンは、本実施の形態に関する半導体装置を構成する領域の平面視における四方を取り囲むように形成されなければならない。

- [0100] 貫通溝のためのレジストパターンを形成する手法としては、たとえば、フォトリソグラフィー技術が用いられる。当該レジストパターンにおいて貫通溝を形成する開口領域307は、ハードマスク306が外部環境に曝される領域であり、一方で、貫通溝が形成される開口領域307以外の領域である非開口領域は、レジストによってハードマスク306が保護される領域である。

- [0101] その後、ステップST305において、外部環境に曝されている開口領域

307に対応するハードマスク306のみが除去される(たとえば、図12を参照)。ハードマスク306の除去手法においては、たとえば、薬液浸漬によるウェットエッチング、または、ドライエッチングが選択される。

- [0102] そして、ハードマスク306を除去した後、さらに、開口領域307のSi 基板301の表面が外部環境に曝されることになる。その後、レジストパターンがハードマスク306から剥離されることによって、非開口領域に対応していたハードマスク306が外部環境に曝されることになる。

- [0103] その後、ステップST306において、外部環境に曝されている開口領域  $307のSi基板301のみが除去される(たとえば、図13を参照)。この手法によって、数百<math>\mu$ mの厚さを有するSi基板301が部分的に除去される。

- [0104] そして、Si基板301が除去された後、開口領域307に対応するGaN層302が外部環境に曝されることになる。一方で、非開口領域では、ステップST306の間、ハードマスク306が完全に除去されることは許されない。

- [0105] その後、ステップST307において、外部環境に曝されている開口領域 307に対応するGaN層302のみが除去される(たとえば、図14を参 照)。GaN層302の除去手法においては、たとえば、数μm以上、かつ 、数十μm以下の厚さに相当するGaN層302が部分的に除去される。

- [0106] そして、GaN層302が除去された後、開口領域307に対応する領域の支持基板305との接合面が外部環境に曝されることになる。一方で、非開口領域では、ステップST307の間、ハードマスク306が完全に除去されることは許されない。

- [0107] ここまでのステップST307までを経て、貫通溝308がGaN-on-Si基板303に形成される。貫通溝308を形成することによって、以下の2つの効果を得ることができる。

- [0108] 1つ目の効果は、本実施の形態に関する特徴的な半導体装置の構造が形成 することができることである。そして、2つ目の効果は、応力開放によって

- 、基板除去工程で生じ得るGaN層302へのクラックまたは割れの発生を抑制することである。

- [0109] その後、ステップST308において、非開口領域のハードマスク306 が除去される。ステップST308におけるハードマスク306の除去手法 には、ドライエッチングの手法を用いることが望ましい。

- [0110] ドライエッチングは、エッチングの進行方法に異方性を有する。また、貫通溝308が形成された領域の側面には、GaN層302およびSi基板301が存在している。そして、これらに対するエッチングの進行を抑制するために、ドライエッチングの手法を用いる。

- [0111] そして、ハードマスク306を除去した後、非開口領域では、島状のSi 基板301が外部環境に曝されることになる。

- [0112] その後、ステップST309において、外部環境に曝されている非開口領域のSi基板301すべてが除去される(たとえば、図15を参照)。Si基板301の除去手法においては、Si基板301を除去した後、GaN層302が外部環境に曝されることになる。

- [0113] この際、エッチング面を平坦化するために、たとえば、化学機械研磨(chemical mechanical polishing、すなわち、CMP)、または、機械研削などの平坦化処理を加えてもよい。

- [0114] その後、ステップST310において、密着層または核形成層を形成する。なお、このステップST310は省略されてもよい。ステップST310を省略することによって得られる半導体装置の構造およびその構成によって生じる効果については、第1の実施の形態および第4の実施の形態において説明されたとおりである。

- [0115] 密着層または核形成層は、ステップST311以降の工程において、ダイヤモンド基板を成長または接合させる際の、密着性を向上させる目的で形成されるものである。

- [0116] 密着層または核形成層の材料としては、たとえば、非晶質Siまたは窒化 Siなどの非晶質材料が一般的に用いられる。しかしながら、たとえば、熱

伝導性に優れるダイヤモンドナノ粒子、ダイヤモンドライクカーボン、グラフェンまたはグラファイトなどが用いられてもよい。

- [0117] また、密着層または核形成層は、貫通溝308の内部にも被覆するように 形成されなければならない。この際、密着層または核形成層の表面を平坦化 するために、たとえば、CMPまたは機械研削などの平坦化処理を加えても よい。

- [0118] その後、ステップST311において、GaN層302の上面および貫通 溝の内部にダイヤモンド層309が形成される(たとえば、図16を参照) 。ダイヤモンド層309の形成手法としては、たとえば、 $CH_4-H_2-O_2$ 系 ガスを用いるマイクロ波CVD法またはホットフィラメントCVD法などの 気相成長、または、ダイヤモンド自立基板との接合方式を用いるとよい。

- [0119] 気相成長であれば、自立するために十分厚膜化しなければならない。一方で、接合法式であれば、貫通溝308に合う自立基板の加工が必要である。

- [0120] このようにして、ダイヤモンド基板の上面の凹部に、GaN層302が形成された構造を作製することができる。形成するダイヤモンドの電気絶縁性は高いことが望ましい。また、ダイヤモンド層309は、貫通溝308の内部を空隙なく完全に充填することが望ましい。

- [0121] 形成されるダイヤモンドの結晶性は、単結晶であっても多結晶であってもよい。また、形成されるダイヤモンドの熱輸送特性は、長距離秩序がある単結晶であるほど優れているため、結晶流は大きく、かつ、高い結晶性を有するものが望ましい。

- [0122] その後、ステップST312において、GaN層302と支持基板305とが遊離される(たとえば、図17を参照)。遊離工程としては、たとえば、薬液を用いるウェットエッチング法を採用するとよい。しかしながら、薬液によって遊離部分以外の構成が損なわれないよう注意すべきである。

- [0123] その後、ステップST313において、GaN層302の表面が環境に曝されることになる。このGaN層302の表面に、たとえば、電極の形成などのデバイスプロセスを施すことによって、本実施の形態に関する半導体装

置の構造を作製することができる。

- [0124] このような半導体装置の構成によれば、Si基板301を全面除去する前に貫通溝308を形成することによって、異種材料の格子不整合に起因する応力開放が分散される。そのため、クラックまたは割れがGaN層302の内部、または、半導体装置の内部に侵入することを抑制することができる。

- [0125] また、電気絶縁性の高いダイヤモンドが貫通溝308の内部に充填される ことによって、ダイヤモンドが素子間分離の機能を担うことができる。これ によって、デバイスプロセスにおいて素子間分離工程を簡略化することがで きる。

- [0126] 素子間分離工程において、たとえば、選択イオン注入プロセスが採用されているとすれば、当該工程を省略することができる。また、選択イオン注入プロセスを省略することによって、たとえば、高温熱履歴が許諾されるなどのプロセス上の自由度を向上させることができる。

- [0127] <第8の実施の形態>

本実施の形態に関する半導体装置、および、半導体装置の製造方法について説明する。以下の説明においては、以上に記載された実施の形態で説明された構成要素と同様の構成要素については同じ符号を付して図示し、その詳細な説明については適宜省略するものとする。

[0128] <半導体装置の構成について>

図8は、図1から図6に例が示された半導体装置の、製造方法の別の例を示すフローチャートである。また、図18から図23は、本実施の形態に関する半導体装置の、製造工程の例を示す断面図である。以下、図8および図18から図23を参照しつつ、本実施の形態に関する半導体装置の製造方法を説明する。

[0129] まず、ステップST401に例が示されるように、本製造方法では、ダイヤモンド自立基板310を出発基板として用意する(たとえば、図18を参照)。本実施の形態で適用されるダイヤモンド自立基板310の電気絶縁性は、高いことが望ましい。また、ダイヤモンド自立基板310の表面を平坦

化するために、たとえば、CMPまたは機械研削などの平坦化処理を加えてもよい。

- [0130] その後、ステップST402において、ダイヤモンド自立基板310の表面に対しハードマスク311を形成する(たとえば、図19を参照)。ハードマスク311は、ドライエッチング耐性があり、かつ、ダイヤモンドに対しエッチングの選択比を有する材料であることが望ましい。ハードマスク311の材料は、たとえば、窒化Si、アルミナ膜または二酸化Siなどであってもよい。

- [0131] これらの材料の形成手法は、たとえば、PVD法またはCVD法などであってもよい。また、ハードマスク311は、1層以上形成される構成であってもよい。

- [0132] その後、ステップST403において、ステップST402で形成された ハードマスク311に対し、ダイヤモンド自立基板310に凹部を形成する ためのレジストパターンを形成する。凹部を形成するためのレジストパター ンは、本実施の形態に関する半導体装置を構成する領域の平面視における四方を取り囲むように形成されなければならない。

- [0133] 凹部を形成するためのレジストパターンを形成する手法としては、たとえば、フォトリソグラフィー技術が用いられる。当該レジストパターンにおいて凹部を形成する開口領域312は、ハードマスク311が外部環境に曝される領域であり、一方で、凹部が形成される開口領域312以外の領域である非開口領域は、レジストによってハードマスク311が保護される領域である。

- [0134] その後、ステップST404において、外部環境に曝されている開口領域 312に対応するハードマスク311のみが除去される(たとえば、図20 を参照)。ハードマスク311の除去手法においては、たとえば、薬液浸漬 によるウェットエッチング、または、ドライエッチングが選択される。

- [0135] そして、ハードマスク311を除去した後、さらに、開口領域312はダイヤモンド自立基板310の表面が外部環境に曝されることになる。その後

、レジストパターンがハードマスク311から剥離されることによって、非 開口領域に対応していたハードマスク311が外部環境に曝されることにな る。

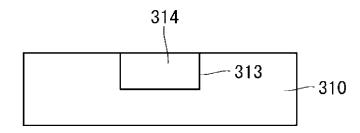

- [0136] その後、ステップST405において、外部環境に曝されている開口領域 312のダイヤモンド自立基板310のみが部分的に除去される。そして、 開口領域312に対応する領域に凹部313が形成される(たとえば、図2 1を参照)。開口領域312のダイヤモンド基板を除去する方法は、この他 、本実施の形態において目的に適合するいかなる除去手法であってもよい。

- [0137] ダイヤモンド自立基板310の除去量は、製造される半導体装置の寸法に合う膜厚に適正に制御されなければならない。そのため、開口領域312のすべてを貫通してダイヤモンド自立基板310を除去することは想定しない。

- [0138] ダイヤモンド自立基板310が部分的に除去された後、開口領域312の ダイヤモンド自立基板310のエッチング面、すなわち、凹部313が外部 環境に曝されることになる。この際、ダイヤモンド自立基板310のエッチ ング面を平坦化するために、たとえば、CMPまたは機械研削などの平坦化 処理を加えてもよい。

- [0139] その後、ステップST406において、外部環境に曝されているダイヤモンド自立基板310のエッチング面、すなわち、凹部313に対し、窒化物半導体層314が形成される(たとえば、図22を参照)。窒化物半導体層314の形成方法としては、たとえば、有機金属化学気相堆積(metalorganic chemical vapor deposition、すなわち、MOCVD)法、または、分子線エピタキシー(molecular beam epitaxy、すなわち、MBE)法などであってもよい。または、J. W. Shonらによって報告されている、グラフェンフィルム上に窒化物半導体を結晶成長させる手法などを用いてもよい(J. W. Shon, J. Ohta, K. Ueno, A. Kobayashi, and H. Fujioka, "Structural Properties

of GaN films grown on multilayer graphene films by pulsed sputtering", Appl. Phys. Express 7, 085502 (2014).)。この他、本実施の形態に関する半導体装置の目的に適合するいかなる結晶成長手法であってもよい。

- [0140] また、窒化物半導体層314は少なくとも1層で構成されるものであればよい。たとえば、HEMTデバイスの場合、2DEGを形成するために電子走行層となる第1のエピタキシャル半導体層と、障壁層となる第2のエピタキシャル半導体層とを形成する。

- [0141] 成長する窒化物半導体層314の厚さは制御されなければならず、かつ、 ダイヤモンド自立基板310の非エッチング面である表面と同じ高さである 必要がある。

- [0142] また、ダイヤモンド自立基板310と窒化物半導体層314との間に、第2の実施の形態または第5の実施の形態で述べられた密着層または核形成層、または、ダイヤモンド自立基板310と窒化物半導体層314との間の格子不整合を緩和する格子緩和層が介在していてもよい。

- [0143] 窒化物半導体層314を形成した後、開口領域312の窒化物半導体層314の表面が外部環境に曝されることになる。この際、窒化物半導体層314の表面を平坦化するために、たとえば、CMPまたは機械研削などの平坦化処理を加えてもよい。

- [0144] その後、ステップST407において、非開口領域であるダイヤモンド自立基板310の表面のハードマスク311が除去される(たとえば、図23を参照)。ステップST407におけるハードマスク311の除去手法は、薬液を用いるウェットエッチングであっても、ドライエッチングであってもよい。

- [0145] 窒化物半導体層314に対し薬液耐性を有する薬液を使うことができる場合、ウェットエッチングの除去手法は窒化物半導体層314への損傷の影響が少なく、かつ、簡便にハードマスク311を除去することができる。

- [0146] その後、ステップST408において、窒化物半導体層314の表面に、 たとえば、電極の形成などのデバイスプロセスを施すことによって、本実施 の形態に関する半導体装置の構造が作製することができる。

- [0147] このような半導体装置の構成によれば、電気絶縁性の高いダイヤモンドが 窒化物半導体層314の平面視における四方を取り囲んでいることによって 、ダイヤモンド自立基板310が素子間分離の機能を担うことができる。こ れによって、デバイスプロセスにおいて素子間分離工程を簡略化することが できる。

- [0148] 素子間分離工程において、たとえば、選択イオン注入プロセスが採用されているとすれば、当該工程を省略することができる。また、選択イオン注入プロセスを省略することによって、たとえば、高温熱履歴が許諾されるなどのプロセス上の自由度を向上させることができる。

- [0149] <以上に記載された実施の形態によって生じる効果について>次に、以上に記載された実施の形態によって生じる効果の例を示す。なお、以下の説明においては、以上に記載された実施の形態に例が示された具体的な構成に基づいて当該効果が記載されるが、同様の効果が生じる範囲で、本願明細書に例が示される他の具体的な構成と置き換えられてもよい。

- [0150] また、当該置き換えは、複数の実施の形態に跨ってなされてもよい。すなわち、異なる実施の形態において例が示されたそれぞれの構成が組み合わされて、同様の効果が生じる場合であってもよい。

- [0151] 以上に記載された実施の形態によれば、半導体装置は、ダイヤモンドからなるダイヤモンド基板23と、窒化物半導体層とを備える。ここで、窒化物半導体層は、たとえば、エピタキシャル半導体層2、エピタキシャル半導体層2 B、エピタキシャル半導体層2 C、エピタキシャル半導体層3 A、エピタキシャル半導体層3 A、エピタキシャル半導体層3 Cのうちの少なくとも1つに対応するものである。そして、エピタキシャル半導体層2 およびエピタキシャル半導体層3は、ダイヤモンド基板23の上面109に形成された凹部17の

内部に形成される。

- [0152] このような構成によれば、高い熱伝導率を有するダイヤモンドが、窒化物 半導体層の下面に加えて側面にも接触して形成されている。そのため、窒化 物半導体層の上面に素子構造などが形成されることによって窒化物半導体層 を含む半導体装置が発熱源となる場合、半導体装置の下方に加えて側方に高 い放熱性能を発揮することができる。したがって、半導体装置の温度上昇を 大幅に抑制することができる。

- [0153] なお、これらの構成以外の本願明細書に例が示される他の構成については 適宜省略することができる。すなわち、少なくともこれらの構成を備えてい れば、以上に記載された効果を生じさせることができる。

- [0154] しかしながら、本願明細書に例が示される他の構成のうちの少なくとも1つを、以上に記載された構成に適宜追加した場合、すなわち、以上に記載された構成としては言及されなかった本願明細書に例が示される他の構成が適宜追加された場合であっても、同様の効果を生じさせることができる。

- [0155] また、以上に記載された実施の形態によれば、エピタキシャル半導体層2 およびエピタキシャル半導体層3は、平面視においてダイヤモンド基板23 の上面109に全周囲を囲まれて形成される。このような構成によれば、半 導体装置の全側方に高い放熱性能を発揮することができる。したがって、半 導体装置の温度上昇を大幅に抑制することができる。

- [0156] また、以上に記載された実施の形態によれば、ダイヤモンド基板23の上面109と、エピタキシャル半導体層3の上面401とが、同一平面上に位置する。このような構成によれば、エピタキシャル半導体層2の側方およびエピタキシャル半導体層3の側方を漏れなくダイヤモンド基板23によって覆うことができるため、半導体装置の側方に高い放熱性能を発揮することができる。

- [0157] また、以上に記載された実施の形態によれば、ダイヤモンド基板23は、 電気絶縁性を有する。このような構成によれば、ダイヤモンド基板23の凸 部16を半導体装置の素子間分離領域として利用することができる。そのた

め、別途素子間分離領域を形成するための工程を設ける必要がなくなり、製造工程を簡略化することができる。

- [0158] また、以上に記載された実施の形態によれば、半導体装置は、ダイヤモンド基板23の凹部17の内壁に形成される、介在層を備える。ここで、介在層は、たとえば、密着層または核形成層19、密着層または核形成層19A、密着層または核形成層19Bおよび密着層または核形成層19Cのうちの少なくとも1つに対応するものである。エピタキシャル半導体層2およびエピタキシャル半導体層3は、密着層または核形成層19を介してダイヤモンド基板23の凹部17の内部に形成される。このような構成によれば、エピタキシャル半導体層2およびエピタキシャル半導体層2およびエピタキシャル半導体層2およびエピタキシャル半導体層2およびエピタキシャル半導体層3を形成した後にそれらを覆うダイヤモンド層を形成する場合に、エピタキシャル半導体層3を形成した後にそれらを覆うダイヤモンド層を形成する場合に、エピタキシャル半導体層3を形成した後にそれらを覆うダイヤモンド層を形成する場合に、エピタキシャル半導体層3を形成した後にそれらを覆うダイヤモンド層を形成する場合に、エピタキシャル半導体層2およびエピタキシャル半導体層3に生じる欠損または損傷を抑制することができる。

- [0159] また、以上に記載された実施の形態によれば、介在層は、ダイヤモンド自立基板310と窒化物半導体層314との間の格子不整合を緩和する格子緩和層である。このような構成によれば、ダイヤモンド自立基板310の凹部313に窒化物半導体層314を形成する場合に、格子不整合を緩和して結晶欠陥の少ない窒化物半導体層314を形成することができる。

- [0160] また、以上に記載された実施の形態によれば、半導体装置は、エピタキシャル半導体層3の上面に形成される電極部を備える。ここで、電極部は、たとえば、ドレイン電極金属101、ドレイン電極金属101B、ドレインまたはソース電極金属102B、ゲート電極金属106およびゲート電極金属106Bのうちの少なくとも1つに対応するものである。このような構成によれば、エピタキシャル半導体層3の上面に素子構造などが形成されることによって半導体装置が発熱源となる

場合、半導体装置の下方に加えて側方に高い放熱性能を発揮することができる。

- [0161] 以上に記載された実施の形態によれば、半導体装置の製造方法において、半導体基板の上面に窒化物半導体層を形成する。ここで、半導体基板は、たとえば、Si基板301に対応するものである。また、窒化物半導体層は、たとえば、GaN層302に対応するものである。そして、GaN層302の表面と支持基板305とを接合する。そして、Si基板301の下面にハードマスク306を形成する。そして、ハードマスク306に開口領域307を有するパターンを形成する。そして、開口領域307に対応するSi基板301、さらには、GaN層302を除去することによって、Si基板301およびGaN層302を貫通する溝308を形成する。そして、ハードマスク306およびSi基板301を除去する。そして、支持基板305の表面に、GaN層302を覆うダイヤモンド層309を形成する。そして、GaN層302の表面およびダイヤモンド層309の表面と、支持基板305とを遊離させる。

- [0162] このような構成によれば、Si基板301を全面的に除去する工程の前に、Si基板301およびGaN層302を貫通する溝308をあらかじめ形成しておくことによって、GaN層302において、応力緩和に起因するクラックまたは割れが生じることを抑制することができる。

- [0163] なお、これらの構成以外の本願明細書に例が示される他の構成については 適宜省略することができる。すなわち、少なくともこれらの構成を備えてい れば、以上に記載された効果を生じさせることができる。

- [0164] しかしながら、本願明細書に例が示される他の構成のうちの少なくとも1つを、以上に記載された構成に適宜追加した場合、すなわち、以上に記載された構成としては言及されなかった本願明細書に例が示される他の構成が適宜追加された場合であっても、同様の効果を生じさせることができる。

- [0165] また、特段の制限がない場合には、それぞれの処理が行われる順序は変更 することができる。

- [0166] また、以上に記載された実施の形態によれば、ダイヤモンドからなるダイヤモンド基板を用意する。ここで、ダイヤモンド基板は、たとえば、ダイヤモンド自立基板310の表面にハードマスク311を形成する。そして、グイヤモンド自立基板310の表面にハードマスク311を形成する。そして、ハードマスク311に開口領域312を有するパターンを形成する。そして、開口領域312に対応するダイヤモンド自立基板310を除去することによって凹部313を形成する。そして、凹部313の内部に窒化物半導体層314をエピタキシャル成長させる。

- [0167] このような構成によれば、商業的にダイヤモンド自立基板310が実現された場合には、本実施形態に関する半導体装置の商業的な製造を簡便に行うことができる。また、商業的にダイヤモンド自立基板310を除去する工程が実現された場合には、本実施形態に関する半導体装置の商業的な製造を簡便に行うことができる。

- [0168] なお、これらの構成以外の本願明細書に例が示される他の構成については 適宜省略することができる。すなわち、少なくともこれらの構成を備えてい れば、以上に記載された効果を生じさせることができる。

- [0169] しかしながら、本願明細書に例が示される他の構成のうちの少なくとも1つを、以上に記載された構成に適宜追加した場合、すなわち、以上に記載された構成としては言及されなかった本願明細書に例が示される他の構成が適宜追加された場合であっても、同様の効果を生じさせることができる。

- [0170] また、特段の制限がない場合には、それぞれの処理が行われる順序は変更 することができる。

- [0171] <以上に記載された実施の形態における変形例について>

以上に記載された実施の形態では、それぞれの構成要素の材質、材料、寸法、形状、相対的配置関係または実施の条件などについても記載する場合があるが、これらはすべての局面においてひとつの例であって、本願明細書に記載されたものに限られることはないものとする。

[0172] したがって、例が示されていない無数の変形例、および、均等物が、本願

明細書に開示される技術の範囲内において想定される。たとえば、少なくとも1つの構成要素を変形する場合、追加する場合または省略する場合、さらには、少なくとも1つの実施の形態における少なくとも1つの構成要素を抽出し、他の実施の形態の構成要素と組み合わせる場合が含まれるものとする

- [0174] さらに、以上に記載された実施の形態におけるそれぞれの構成要素は概念的な単位であって、本願明細書に開示される技術の範囲内には、1つの構成要素が複数の構造物から成る場合と、1つの構成要素がある構造物の一部に対応する場合と、さらには、複数の構成要素が1つの構造物に備えられる場合とを含むものとする。

- [0175] また、以上に記載された実施の形態におけるそれぞれの構成要素には、同一の機能を発揮する限り、他の構造または形状を有する構造物が含まれるものとする。

- [0176] また、本願明細書における説明は、本技術に関するすべての目的のために 参照され、いずれも、従来技術であると認めるものではない。

- [0177] また、以上に記載された実施の形態において、特に指定されずに材料名などが記載された場合は、矛盾が生じない限り、当該材料に他の添加物が含まれた、たとえば、合金などが含まれるものとする。

#### 符号の説明

[0178] 2, 2A, 2B, 2C, 3, 3A, 3B, 3C エピタキシャル半導体層、16, 16A, 16B, 16C, 16D 凸部、17, 17A, 17B, 17C, 313 凹部、19, 19A, 19B, 19C 密着層または核形成層、21, 21A, 21B, 21C, 24, 24A, 24B, 24C, 28, 28B 接合界面、23, 23A, 23B, 23C ダイヤモンド基板、25, 25B 下面、101, 101B ドレイン電極金属、102, 1

02B ドレインまたはソース電極金属、105,105B 表面保護膜、106,106B ゲート電極金属、107 ソースまたはドレインパッド電極金属、108 ドレインまたはソースパッド電極金属、109,109B,401,401A,401B,401C 上面、201 電界効果トランジスタ、201B マルチフィンガー型HEMT、202,202B 素子間分離領域、301 Si基板、302 GaN層、303 GaNーのn-Si基板、305 支持基板、306,311 ハードマスク、307,312 開口領域、308 貫通溝、309 ダイヤモンド層、310 ダイヤモンド自立基板、314 窒化物半導体層。

# 請求の範囲

[請求項1] ダイヤモンドからなるダイヤモンド基板(23)と、

前記ダイヤモンド基板(23)の上面(109)に形成された凹部(17)の内部に形成される窒化物半導体層(2、3)とを備える、半導体装置。

[請求項2] 前記窒化物半導体層(2、3)は、平面視において前記ダイヤモンド基板(23)の前記上面(109)に全周囲を囲まれて形成される

•

請求項1に記載の半導体装置。

[請求項3] 前記ダイヤモンド基板(23)の前記上面(109)と、前記窒化 物半導体層(2、3)の上面(401)とが、同一平面上に位置する

•

請求項1または請求項2に記載の半導体装置。

[請求項4] 前記ダイヤモンド基板(23)は、電気絶縁性を有する、

請求項1から請求項3のうちのいずれか1項に記載の半導体装置。

[請求項5] 前記ダイヤモンド基板(23)の前記凹部(17)の内壁に形成される、介在層(19)をさらに備え、

前記窒化物半導体層(2、3)は、前記介在層(19)を介して前記ダイヤモンド基板(23)の前記凹部(17)の内部に形成される

`

請求項1から請求項4のうちのいずれか1項に記載の半導体装置。

[請求項6] 前記介在層(19)は、前記ダイヤモンド基板(23)と前記窒化物半導体層(2、3)との間の格子不整合を緩和する格子緩和層である、

請求項5に記載の半導体装置。

[請求項7] 前記窒化物半導体層(2、3)の上面に形成される電極部(101 、102、106)をさらに備える、

請求項1から請求項6のうちのいずれか1項に記載の半導体装置。

[請求項8] 半導体基板(301)の上面に窒化物半導体層(302)を形成し

前記窒化物半導体層(302)の表面と支持基板(305)とを接合し、

前記半導体基板(301)の下面にハードマスク(306)を形成し、

前記ハードマスク(306)に開口領域(307)を有するパターンを形成し、

前記開口領域(307)に対応する前記半導体基板(301)、さらには、前記窒化物半導体層(302)を除去することによって、前記半導体基板(301)および前記窒化物半導体層(302)を貫通する溝(308)を形成し、

前記ハードマスク(306)および前記半導体基板(301)を除去し、

前記支持基板(305)の表面に、前記窒化物半導体層(302) を覆うダイヤモンド層(309)を形成し、

前記窒化物半導体層(302)の表面および前記ダイヤモンド層(309)の表面と、前記支持基板(305)とを遊離させる、

半導体装置の製造方法。

を形成し、

[請求項9] ダイヤモンドからなるダイヤモンド基板(310)を用意し、 前記ダイヤモンド基板(310)の表面にハードマスク(311)

前記ハードマスク(311)に開口領域(312)を有するパターンを形成し、

前記開口領域(312)に対応する前記ダイヤモンド基板(310)を除去することによって凹部(313)を形成し、

前記凹部(313)の内部に窒化物半導体層(314)をエピタキシャル成長させる、

半導体装置の製造方法。

[図7]

# [図23]

### INTERNATIONAL SEARCH REPORT

International application No.

PCT/JP2018/024584

## A. CLASSIFICATION OF SUBJECT MATTER

Int. Cl. H01L21/338(2006.01)i, H01L29/778(2006.01)i, H01L29/812(2006.01)i

According to International Patent Classification (IPC) or to both national classification and IPC

#### B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

Int. Cl. H01L21/338, H01L29/778, H01L29/812

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Published examined utility model applications of Japan 1922-1996

Published unexamined utility model applications of Japan 1971-2018

Registered utility model specifications of Japan 1996-2018

Published registered utility model applications of Japan 1994-2018

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

#### C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                           | Relevant to claim No.   |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| X<br>A    | JP 2007-096130 A (TOSHIBA CORP.) 12 April 2007, paragraphs [0037], [0042]-[0053], fig. 5-7 & US 2007/0114539 A1, paragraphs [0051], [0056]-[0067], fig. 5-7 & CN 1941438 A   | 1, 5, 7<br>2-4, 6, 8, 9 |

| A         | JP 2018-041785 A (FUJITSU LTD.) 15 March 2018, paragraphs [0019]-[0026], [0051]-[0056], fig. 11-15 & US 2018/0068923 A1, paragraphs [0042]-[0049], [0074]-[0079], fig. 11-15 | 1-9                     |

| А         | JP 2015-065233 A (MITSUBISHI ELECTRIC CORP.) 09 April 2015, paragraph [0029], fig. 8 & US 2015/0084103 A1, paragraph [0038], fig. 8 & DE 102014213565 A1 & CN 104465770 A    | 1-9                     |

| Further documents are listed in the continuation of Box C.                                                                                                                                                                                            | See patent family annex.                                                                                                                                                                            |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| * Special categories of cited documents:  "A" document defining the general state of the art which is not considered to be of particular relevance                                                                                                    | "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention |  |

| "E" earlier application or patent but published on or after the international filing date  "L" document which may throw doubts on priority claim(s) or which is                                                                                       | "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone                        |  |

| "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)  "O" document referring to an oral disclosure, use, exhibition or other means | "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination |  |

| "P" document published prior to the international filing date but later than the priority date claimed                                                                                                                                                | being obvious to a person skilled in the art  "&" document member of the same patent family                                                                                                         |  |

| Date of the actual completion of the international search 18.07.2018                                                                                                                                                                                  | Date of mailing of the international search report 31.07.2018                                                                                                                                       |  |

| Name and mailing address of the ISA/ Japan Patent Office 3-4-3, Kasumigaseki, Chiyoda-ku,                                                                                                                                                             | Authorized officer                                                                                                                                                                                  |  |

| Tokyo 100-8915, Japan                                                                                                                                                                                                                                 | Telephone No.                                                                                                                                                                                       |  |

# INTERNATIONAL SEARCH REPORT

International application No.

PCT/JP2018/024584

| Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                                                                                     |                       |  |  |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|

| Category*                                          | Citation of document, with indication, where appropriate, of the relevant passages                                                                                  | Relevant to claim No. |  |  |

| A                                                  | JP 2012-084653 A (ADVANCED POWER DEVICE RESEARCH ASSOCIATION) 26 April 2012, paragraphs [0030]- [0041], [0060]-[0070], fig. 5, 15-19 (Family: none)                 | 1-9                   |  |  |

| А                                                  | JP 2012-084781 A (INDEPENDENT ADMINISTRATIVE INSTITUTION NATIONAL INSTITUTE FOR MATERIALS SCIENCE) 26 April 2012, paragraphs [0025]-[0069], fig. 1-4 (Family: none) | 1-9                   |  |  |

| A                                                  | <pre>JP 2016-139695 A (TOSHIBA CORP.) 04 August 2016, paragraphs [0008]-[0022], [0057]-[0063], fig. 1, 5, 11, 12 (Family: none)</pre>                               | 1-9                   |  |  |

|                                                    |                                                                                                                                                                     |                       |  |  |

|                                                    |                                                                                                                                                                     |                       |  |  |

Α. 発明の属する分野の分類(国際特許分類(IPC))

Int.Cl. H01L21/338(2006.01)i, H01L29/778(2006.01)i, H01L29/812(2006.01)i

### 調査を行った分野

調査を行った最小限資料(国際特許分類(IPC))

Int.Cl. H01L21/338, H01L29/778, H01L29/812

最小限資料以外の資料で調査を行った分野に含まれるもの

日本国実用新案公報 1922-1996年

1971-2018年 日本国公開実用新案公報

日本国実用新案登録公報 1996-2018年 日本国登録実用新案公報 1994-2018年

国際調査で使用した電子データベース (データベースの名称、調査に使用した用語)

#### Lc. 関連すると認められる文献

| C.                      |                                                                                                                                                 |                         |  |  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|

| 引用文献の<br>カテゴリー <b>*</b> | 引用文献名 及び一部の箇所が関連するときは、その関連する箇所の表示                                                                                                               | 関連する<br>請求項の番号          |  |  |

| X<br>A                  | JP 2007-096130 A (株式会社東芝)<br>2007.04.12,段落[0037],[0042]-[0053],図 5-7<br>& US 2007/0114539 A1,段落[0051],[0056]-[0067],図 5-7<br>& CN 1941438 A     | 1, 5, 7<br>2-4, 6, 8, 9 |  |  |

| A                       | JP 2018-041785 A(富士通株式会社)<br>2018.03.15,段落[0019]-[0026],[0051]-[0056],図 11-15<br>& US 2018/0068923 A1,段落[0042]-[0049],[0074]-[0079],<br>図 11-15 | 1-9                     |  |  |

### C欄の続きにも文献が列挙されている。

パテントファミリーに関する別紙を参照。

- \* 引用文献のカテゴリー

- 「A」特に関連のある文献ではなく、一般的技術水準を示す 「T」国際出願日又は優先日後に公表された文献であって もの

- 「E」国際出願日前の出願または特許であるが、国際出願日 以後に公表されたもの

- 「L」優先権主張に疑義を提起する文献又は他の文献の発行 日若しくは他の特別な理由を確立するために引用す る文献(理由を付す)

- 「O」口頭による開示、使用、展示等に言及する文献

- 「P」国際出願日前で、かつ優先権の主張の基礎となる出願

- の日の後に公表された文献

- 出願と矛盾するものではなく、発明の原理又は理論 の理解のために引用するもの

- 「X」特に関連のある文献であって、当該文献のみで発明 の新規性又は進歩性がないと考えられるもの

- 「Y」特に関連のある文献であって、当該文献と他の1以 上の文献との、当業者にとって自明である組合せに よって進歩性がないと考えられるもの

- 「&」同一パテントファミリー文献

国際調査報告の発送日 国際調査を完了した日 18.07.2018 31.07.2018 5 F 5896 特許庁審査官(権限のある職員) 国際調査機関の名称及びあて先 日本国特許庁(ISA/JP) 恩田 和彦 郵便番号100-8915 電話番号 03-3581-1101 内線 東京都千代田区霞が関三丁目4番3号 3516

| C (続き). 関連すると認められる文献    |                                                                                                                                     |                |  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------|--|

| 引用文献の<br>カテゴリー <b>*</b> | 引用文献名 及び一部の箇所が関連するときは、その関連する箇所の表示                                                                                                   | 関連する<br>請求項の番号 |  |

| A                       | JP 2015-065233 A(三菱電機株式会社)<br>2015.04.09,段落[0029],図 8<br>& US 2015/0084103 A1,段落[0038],図 8<br>& DE 102014213565 A1 & CN 104465770 A | 1-9            |  |

| A                       | JP 2012-084653 A(次世代パワーデバイス技術研究組合)<br>2012.04.26, 段落[0030]-[0041],[0060]-[0070],図 5,15-19<br>(ファミリーなし)                              | 1-9            |  |

| A                       | JP 2012-084781 A(独立行政法人物質・材料研究機構)<br>2012.04.26, 段落[0025]-[0069],図 1-4<br>(ファミリーなし)                                                 | 1-9            |  |

| A                       | JP 2016-139695 A (株式会社東芝) 2016.08.04, 段落[0008]-[0022], [0057]-[0063], 図 1, 5, 11, 12 (ファミリーなし)                                      | 1-9            |  |

|                         |                                                                                                                                     |                |  |