# (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

# (19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO 2019/068919 A1

# (43) International Publication Date 11 April 2019 (11.04.2019)

- (51) International Patent Classification: *H01L 21/02* (2006,01)

- (21) International Application Number:

PCT/EP2018/077233

(22) International Filing Date:

05 October 2018 (05.10.2018)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

17195086.8

05 October 2017 (05.10.2017) EF

- (71) Applicant: HEXAGEM AB [SE/SE]; Blomstergården 15, 245 62 Hjärup (SE).

- (72) Inventors: OHLSSON, Jonas; Kungsgatan 33 C, 212 13 Malmö (SE). SAMUELSON, Lars; Isbergs gata 28, 211 19 Malmö (SE). STORM, Kristian; Blomstergården 15, 245 62 Hjärup (SE). CIECHONSKI, Rafal; Nordanväg 20, 1gh 1404, 222 28 Lund (SE). MARKUS, Bart; c/o Hexagem AB, Blomstergården 15, 245 62 Hjärup (SE).

- (74) Agent: NEIJ & LINDBERG AB; Pedellgatan 11, 224 60 Lund (SE).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DJ, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JO, JP, KE, KG, KH, KN, KP, KR, KW, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA,

- SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

#### Published:

- with international search report (Art. 21(3))

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments (Rule 48.2(h))

(54) Title: SEMICONDUCTOR DEVICE HAVING A PLANAR III-N SEMICONDUCTOR LAYER AND FABRICATION METHOD

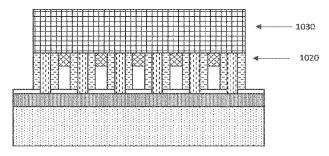

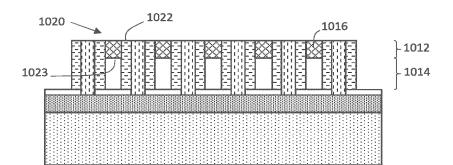

Fig. 12

(57) **Abstract:** A semiconductor device having a planar III-N semiconductor layer, comprising a substrate comprising a wafer (101) and a buffer layer (102), of a buffer material different from a material of the wafer, the buffer layer having a growth surface (1021); an array of nano structures (1010) epitaxially grown from the growth surface; a continuous planar layer (1020) formed by coalescence of upper parts of the nano structures at an elevated temperature T, wherein the number of lattice cells spanning a center distance between adjacent nano structures are different at the growth surface and at the coalesced planar layer; a growth layer (1030), epitaxially grown on the planar layer (1020).

1

# SEMICONDUCTOR DEVICE HAVING A PLANAR III-N SEMICONDUCTOR LAYER AND FABRICATION METHOD

# 5 FIELD OF THE INVENTION

The present invention relates to III-nitride semiconductor substrates and methods for forming a planar surface on such substrates. More particularly, the invention relates to designs and processes for forming a planar surface of a c-oriented, fully relaxed and dislocation-free, III-nitride material, suitable to serve as a template for carrying electronic or optical components.

#### **BACKGROUND**

10

15

20

25

30

Semiconductor wafers are typically fabricated by liquid phase epitaxy, most often the Czochralski-method, already invented in 1916 by Jan Czochralski. In the Czhochralski-process thermally induced precipitation of liquid state material to a solid state crystal is realized by slowly pulling a monocrystalline seed from a hot liquid melt.

While epitaxial growth requires a certain deviation from thermal equilibrium in order to drive continuous crystallization, LPE is carried out at the verge of thermal equilibrium, the main enabler being the similar density of the liquid and the solid state crystal, eliminating diffusion-limitations dominating vapor phase epitaxy where the source material is comparatively dilute in the non-crystalline phase and allowing a minimal deviation from the melting temperature to instigate crystal growth. When the temperature of the system is uniform and the system is in equilibrium the atomic sticking-rate (rate of precipitation) equals the atomic dissociation rate. "Perfect Crystal" growth-conditions above are established when the incorporation of adatoms at crystal lattice sites offer a sufficiently higher decrease in free energy than the incorporation of adatoms at positions of interstitials and vacancies [See Handbook of crystal growth IA Chapters 2 and 8]. In contrast, growth methods far away from thermal equilibrium, such as metal organic vapour phase epitaxy (MOVPE or MOCVD), epitaxial growth is largely limited and governed by the diffusion of source material to the crystal surface and the energy difference between atomic incorporation at perfect lattice sites versus an interstitial site or the creation of a vacancy are insignificant.

2

The Czochralski-process is the predominantly used method for fabrication of semiconductor wafers used by the semiconductor industry and crystal growth by a liquid/solid phase transition, liquid phase epitaxy (LPE), is still the only established method for fabrication-method of high perfection large diameter semiconductor crystal wafers, be it Si, Ge, GaAs, GaP, or InP semiconductors [Handbook of Crystal Growth IIA, Chapter 2]. Crystal defects, such as impurities, vacancies and crystal dislocations can, already at extremely low concentrations, deteriorate electrical and optical properties of the semiconductor. Over hundred years there is little that has changed within the basic fabrication of semiconductor material and the designation of Jan Czochralsiki as "The father of Semiconductor technology" is as valid today as it was then.

5

10

15

20

25

30

The group of binary III-V semiconductors comprising GaN, AlN, InN and their ternary and quaternary alloys are usually simply referred to as "nitrides". The nitrides are unique in their span of properties and potential use. Based on theoretical properties alone, the nitrides comprise the most efficient semiconductor alternatives for high power, radio frequency, and the only viable alternative for true RGB white light-sources and short wavelength LEDs and Lasers from violet through UV. They are, however, also unique in being the only commonly used semiconductors where LPE isn't used to produce wafers. Instead they are usually fabricated by mismatched growth on other crystal substrates, such as SiC, Sapphire and Si wafers. This is unfortunate, since the mismatched crystal growth generates high densities of crystal dislocations,

The predominant challenge for making high perfection semiconductor nitrides is the inability to establish epitaxial conditions close to thermal equilibrium. This is a result of the impossibility to create and contain liquid GaN. The melting point of GaN has been known to be high but it was not until recently that work showed the conditions needed to form congruent GaN melt, at 6 Gigapascal (GPa) and a temperature of 2700 °C [Utsumi et al., Nature Materials, 2, 235, 2003].

Alternative methods for fabricating bulk GaN have been developed, such as ammonothermal growth, solution based growth and HVPE, each with their own advantages [Technology of GaN Crystal Growth, Ehrentraut, Meissner and Bockowski, Springer, 2010]. While they all and together represent great strides forward to an extremely challenging system, they all rely on transport mechanism and comes short of the previously discussed ideal equilibrium conditions of a pure liquid-solid system

3

where the similar density of the liquid and solid phase ensures immediate access to growth species at the growth site, unrestricted by diffusion. Nowadays, there are commercially available small sized bulk GaN, having dislocation densities lower than  $10E5cm^{-2}$ , although at very high price levels and limited quantities.

5

10

15

20

25

30

Epitaxial growth of nitride device layers, are generally carried out by MOCVD. Modern MOCVD reactors are able to accommodate multiple 8" wafers in one run and sustains LED market through GaN/InGaN blue LEDs, and certain niches of power and RF electronics through AlGaN/GaN HEMT structures. In all but the most esoteric application, the base GaN layers and device layers are grown in a single MOCVD-sequence, on foreign substrates, SiC, Sapphire or Si. These substrates are all different from GaN in crystal structure and lattice-size with the introduction of misfit induced lattice dislocations penetrating the device layers as an inevitable consequence.

For various types of electronic devices, such as HEMT (high electron mobility transistor) or HFET (heterojunction field effect transistor) structures, III-nitride materials such as Gallium nitride (GaN) material have superior properties with regard to e.g. electron mobility (speed, efficiency) and high voltage ability than both Si-based materials. However, GaN technology generally entail higher cost than Si technology, and is often inferior in material quality and high voltage reliability compared to e.g. SiC technology. This due to the use of foreign substrates necessitated by inability to fabricate sufficient production levels of GaN native substrates at commercially viable cost levels, and to the fact that no alternative substrate material has properties compatible with the growth of III-nitrides. Thus, major limits of GaN electronics technology boil down to material crystal dislocations and wafer production cost, related to minimization of dislocations originating from growth on foreign substrates, such as SiC.

Various solutions to these problems were suggested by one of the instant inventors in the US patent application 14/378,063, published as US2015/0014631, the content of which is incorporated herein in its entirety by reference. In that application, a method for making a semiconductor device was described, including steps for forming a plurality of semiconductor nanowires over a substrate through an insulating growth mask located over a substrate, forming a semiconductor volume element on each nanowire, planarizing each volume element to form a plurality of discreet III-nitride semiconductor mesas having substantially planar upper surfaces, and forming a device

WO 2019/068919

5

10

15

20

25

30

PCT/EP2018/077233

in each of the plurality of base elements. Each mesa has a substantially planar c-plane {0001} upper surface. The device may also include at least one electrode located over each semiconductor mesa. The process for planarizing grown III-nitride elements is proposed to include in situ etch back of a pyramidical structure, as obtained at the volume growth, by etching or polishing, to form a wide c-plane parallel to the substrate.

#### SUMMARY OF THE INVENTION

Various embodiments within the scope of the invention are defined in the claims. Other objects, advantages and novel features of the invention will become apparent from the following detailed description of the invention when considered in conjunction with the accompanying drawings and claims.

According to one aspect, a method is provided for fabricating a semiconductor device having a planar III-N semiconductor layer, comprising

providing a substrate comprising a wafer, a buffer layer of a different material than the wafer and having a growth surface, and a mask layer on the growth surface, having an array of nanosized apertures;

epitaxially growing a III-N material in the apertures to form nanostructures, such that threading dislocations divert away from a growth front normal to the growth surface;

coalescing upper parts of the nanostructures at an elevated temperature T to form a continuous planar layer;

epitaxially growing a III-N growth layer on said planar layer;

wherein the growth layer is configured such that thermal expansion between RT and T of the growth layer is

- greater than thermal expansion of the substrate when the crystal lattice spacing parallel with the growth surface is smaller in the growth layer than at the growth surface of the buffer layer, and

- lesser than thermal expansion of the substrate when the crystal lattice spacing parallel with the growth surface is larger in the of the growth layer than at the growth surface of the buffer layer.

The mask layer may be removed in subsequent steps, e.g. by etching under influence of an electric field or current.

5

15

25

30

In one embodiment, a nominal lattice constant of the growth layer is adapted by composition configuration of a III-N material in the growth layer.

In one embodiment, T> the sublimation temperature of the III-N material of the nanostructures.

In one embodiment, the growth layer is grown to a thickness of  $>3\mu$ m, or  $>5\mu$ m, or  $>7\mu$ m, or  $>10\mu$ m. The Growth lay may comprise sublayers of varying composition of e.g. different III-N materials.

In one embodiment, the nanostructures comprise GaN.

In one embodiment, the growth layer comprises AlGaN.

In one embodiment, the wafer comprises sapphire.

In one embodiment, the growth layer includes AlGaN, where Al is comprised to >20% of the III materials Ga and Al, or >30% or >40%.

In one embodiment, the growth layer includes AlGaN, where Al is comprised to >45% of the III materials Ga and Al.

In one embodiment, the growth layer comprises InGaN.

In one embodiment, the wafer comprises Si or SiC.

In one embodiment, the upper part of the nanostructures starts between 0 and 200 nm above the mask. The upper part may be defined as a top region of a nanostructure comprising a nanowire.

In one embodiment, the nanostructures include nanowires, grown through said apertures.

In one embodiment, the step of coalescing the upper part of the nanostructures includes providing a background flow of a nitrogen source.

In one embodiment, the step of coalescing involves adding a III-N material between the nanostructures, including an amount of III material which exceeds an amount of III material provided by a source flow of III-material.

In one embodiment, the step of coalescing involves forming III-N material between the nanostructures without a source flow of III-material.

In one embodiment, >90% of the upper parts of the nanostructures are free from threading dislocations. In other embodiments to 99% of the upper parts of the nanostructures are free from threading dislocations, and with decreasing aperture size in the mask, the nanostructures will asymptotically become dislocation free.

In one embodiment, the step of coalescing includes

5

10

15

20

25

30

releasing column III material from the upper ends of the nanostructures;

filling out a spacing between upper parts of m plane facets of the nanostructures, by forming semiconductor material from the released column III material.

In one embodiment, the step of coalescing includes;

leaving a void, not filled with semiconductor material, between the semiconductor structures at lower parts of the m plane facets, adjacent the growth surface.

In one embodiment, said aperture size is <150nm, and/or a spacing between adjacent apertures is  $<2.5\mu$ m.

In one embodiment, thermal expansion of the wafer from RT to T affects built-in crystal strain in the buffer layer and causes an increase in said crystal lattice spacing at the growth surface to deviate from a corresponding increase of a relaxed crystal of the buffer material;

wherein the number of lattice cells spanning the distance between adjacent apertures are different at the growth surface and at the coalesced planar layer.

In one embodiment, the coalesced planar layer has a mean lattice spacing corresponding to it being formed at the elevated temperature, T, with the nominal lattice spacing of an essentially relaxed III-N crystal of the buffer layer material.

According to a second aspect, a semiconductor device having a planar III-N semiconductor layer is provided, comprising

a substrate comprising a wafer and a buffer layer, of a different material than the wafer, having a growth surface;

an array of nanostructures epitaxially grown from the growth surface;

a continuous planar layer formed by coalescence of upper parts of the nanostructures at an elevated temperature T;

a growth layer, epitaxially grown on the planar layer;

wherein crystal lattice spacing parallel with the growth surface is smaller in the growth layer than at the growth surface of the buffer layer; and

wherein the growth layer is configured such that thermal expansion between RT and T is greater for the growth layer than for the substrate.

In one embodiment, the device is characterized in accordance with any of the preceding embodiments.

According to a second aspect, a semiconductor device having a planar III-N semiconductor layer is provided, comprising

WO 2019/068919

5

10

15

20

25

30

a substrate comprising a wafer and a buffer layer, of a different material than the wafer, having a growth surface;

an array of nanostructures epitaxially grown from the growth surface; a continuous planar layer formed by coalescence of upper parts of the nanostructures at an elevated temperature T;

a growth layer, epitaxially grown on the planar layer;

wherein crystal lattice spacing parallel with the growth surface is larger in the growth layer than at the growth surface of the buffer layer (102); and

wherein the growth layer is configured such that thermal expansion between RT and T is lesser for the growth layer for the wafer.

The growth layer may have a planar upper surface. In various embodiments, the semiconductor device may comprise an electrical and/or optical component, formed on the upper surface of the growth layer.

In one embodiment, the electronic device is further characterized in accordance with any of the preceding claims embodiments.

In one embodiment, the number of lattice cells spanning the distance between adjacent apertures are different at the growth surface and at the coalesced planar layer.

In one embodiment, the coalesced planar layer has a mean lattice spacing corresponding to it being formed at the elevated temperature, T, with the nominal lattice spacing of an essentially relaxed III-N crystal of the buffer layer material.

According to a fourth aspect, a semiconductor device having a planar III-N semiconductor layer is provided, comprising

a substrate comprising a wafer and a buffer layer of a buffer material different from a material of the wafer, the buffer layer having a growth surface;

an array of nanostructures epitaxially grown from the growth surface;

a continuous planar layer formed by coalescence of upper parts of the nanostructures at an elevated temperature T, wherein the number of lattice cells spanning a center distance between adjacent nanostructures are different at the growth surface and at the coalesced planar layer;

a growth layer, epitaxially grown on the planar layer. The planar layer may be of the same III-N material as the buffer material.

8

WO 2019/068919 PCT/EP2018/077233

#### BRIEF DESCRIPTION OF THE DRAWINGS

5

25

Preferred embodiments of the invention will now be described with reference to the accompanying drawings.

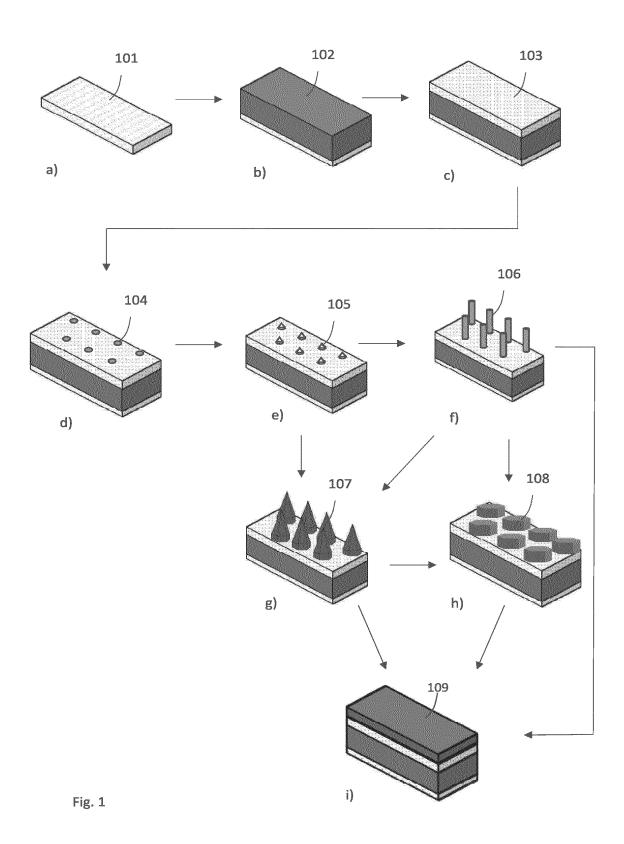

- Fig. 1 schematically illustrates various devices and steps of a production process for a III-nitride semiconductor device according to different embodiments.

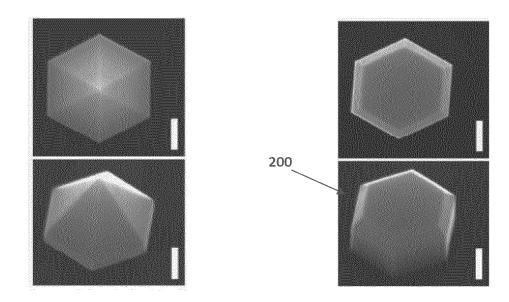

- Figs 2A and B illustrate embodiments of different stages of a GaN device in production.

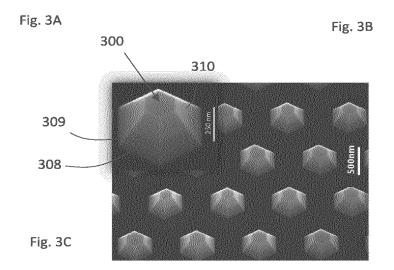

- Figs 3A-C illustrate embodiments of different stages of an InGaN device in production.

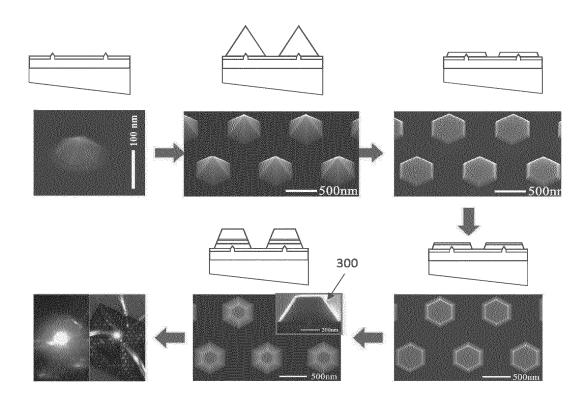

- Fig. 4 schematically illustrate process steps of a production process of an InGaN-based light-emitting component.

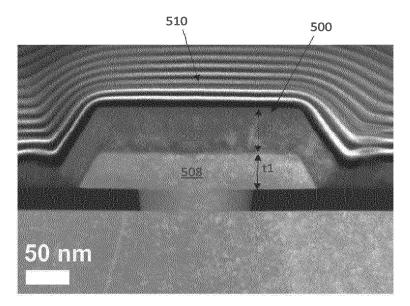

- Fig. 5 shows a side view of an AlGaN device with further epitaxial layers built on top.

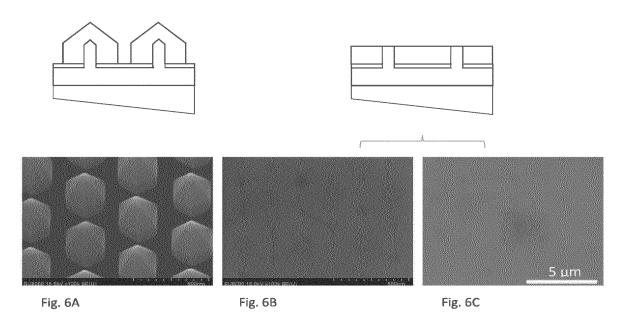

- Figs 6A-C illustrate the formation of a coalesced GaN planar film prepared from discrete GaN nanowire growths.

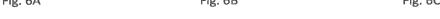

- Figs 6D-E illustrate a subsequently grown GaN film layer on a coalesced GaN film.

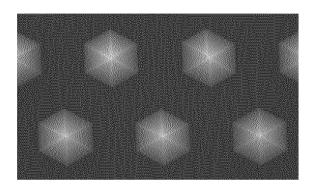

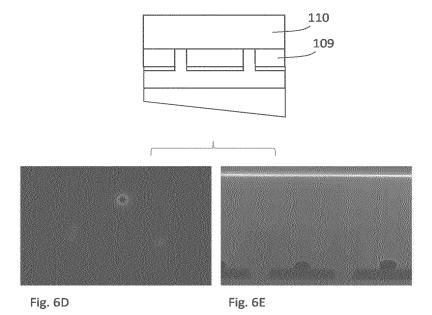

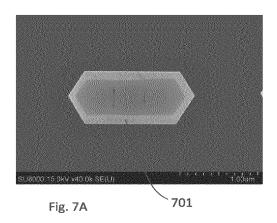

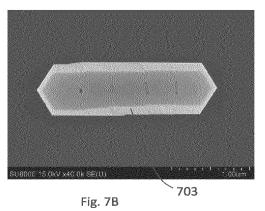

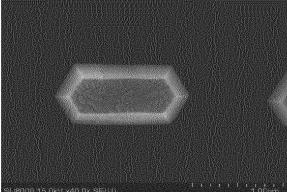

- Figs 7A-B show examples of coalesced planar structures obtained by merging a plurality of separate volume elements.

- Fig. 8A shows an example of a coalesced InGaN layer.

- Fig. 8B shows an example of a coalesced InGaN structure formed from a group of three separate growths.

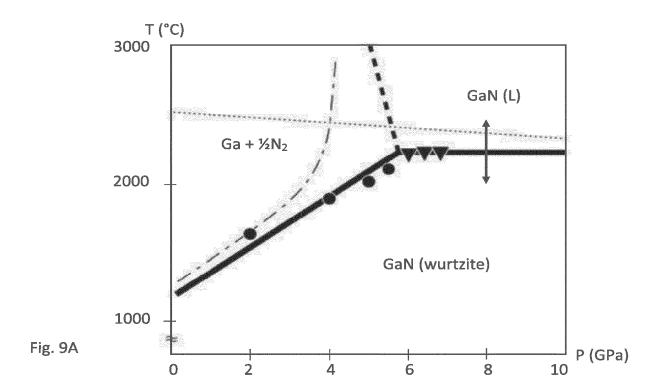

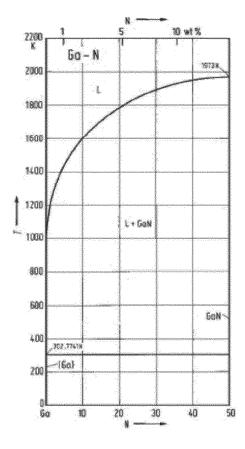

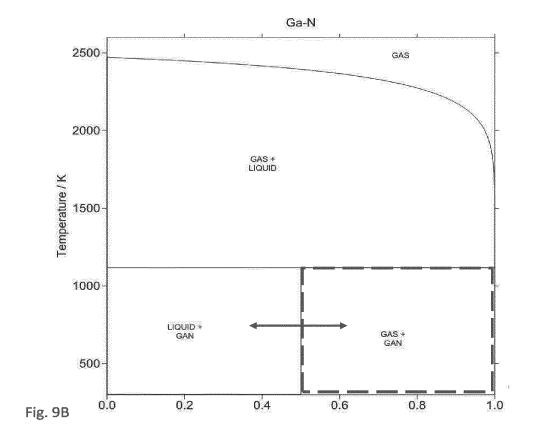

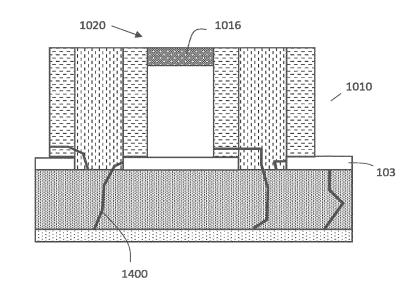

- Figs 9A-C illustrate various Ga-N binary phase diagrams.

- Figs 10A-D illustrate the formation of a nanowire structures for use in a method for making a semiconductor device having a planar layer.

- Fig. 11 shows an embodiment of a semiconductor device including a nanostructure comprising a planar layer of a III-nitride semiconductor crystal.

- Fig. 12 shows an embodiment of a semiconductor device of claim 11, provided with an additional layer.

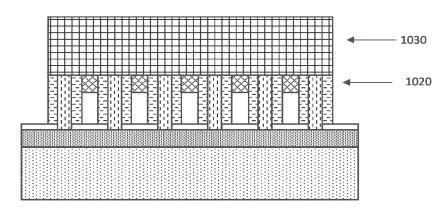

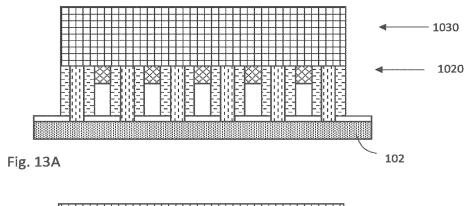

- Figs 13A and B illustrate further processed semiconductor devices of the embodiment of Fig. 12.

- Fig. 14 illustrates threading dislocations in a semiconductor device.

9

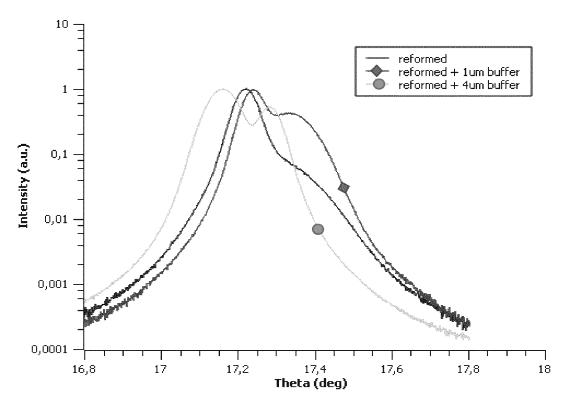

Fig. 15 illustrates x-ray diffraction (XRD) measurements of three different samples of coalesced planar layer fabricated on growth substrates according to various embodiments.

#### 5 DETAILED DESCRIPTION

10

15

20

25

30

Certain embodiments of the invention relate to methods of making a III-nitride semiconductor device. This III-nitride material may e.g. be GaN, InGaN (Indium Gallium nitride), or AlGaN (Aluminum Gallium nitride). The method may comprise forming a plurality of semiconductor seeds over a substrate. The substrate may be any suitable material for growing III-nitride seeds or nanowires, for example a GaN, silicon, SiC, sapphire or AlN wafer which may optionally contain one or more buffer layers, such as a GaN buffer layer on a silicon substrate. For homogeneous fabrication of GaN wafers and arrays the basic atomic information the substrate material provides to the process is a uniform crystal orientation to all seeds and a competitive surface for selective nucleation of GaN. Such a surface may be provided through thin films, such as graphene, ALD-fabricated oxides and LPCVD-fabricated AlN. In various embodiments, the seeds are continuously grown to nanowires. In various embodiments, a semiconductor volume element is grown on each seed or nanowire. In a planarizing step, a plurality of discrete templates, or base elements, having a substantially planar upper surface, are formed. After planarizing, a step of c-plane surface repair growth may also be performed. Subsequent steps may include forming a device, such as an electronic component, in or on each of the plurality of base elements.

As will be discussed, the planarizing step is most appropriately also called a reformation-step. It's our understanding that the large-scale homogeneity seen in the reformation step discussed herein is enabled by homogeneous crystal structure of the dislocation-free crystal templates used. Hitherto, the only known way to provide such an array of dislocation-free templates is through selective NW- growth. Furthermore, a fundamental level it is understood that the dislocation-free nature of the array is dependent on combination of the aperture dimension of the opening in the mask and the specific epitaxial growth conditions. NW growth conditions are no magic bullet but has been shown to provide such dislocation-free crystals. Since the generation of dislocation-free crystals is the prominent task of the NW growth step and, for the

10

purpose of this application, any epitaxial conditions that provides such monocrystalline templates are considered to be NW-conditions.

Different embodiments will now be discussed with reference to the drawings. It shall be noted that reference is made to certain examples of devices and methods, where materials and process parameters of working embodiments are given. This does not, as such, mean that certain steps or features may be of a different character or art without departing from the general scope of the solutions proposed herein, and which fall within the scope of the appended claims. In addition, more details related to e.g. nanowire growth in III-nitride materials are available to the skilled person in e.g. the above-referenced prior application.

5

10

15

20

25

30

Fig. 1 schematically illustrates method step of the production of a III-nitride semiconductor device. In a step a) a base substrate 101 of e.g. sapphire is provided. In a step b) one or more layers 102 of e.g. GaN are formed on the base substrate 101. Together, the layers 101 and 102 form a substrate. In a step c) a mask layer 103 of e.g. SiN<sub>x</sub> may be formed on top of the substrate. In a subsequent step d), holes 104 are provided in the mask layer 103, e.g. by means of EBL (electron beam lithography). The holes may be very narrow, e.g. with a diameter of 50-150 nm, or 60-100 nm. The pitch between the holes 104 may e.g. be in the order of 200-2000 nm, and is selected dependent on inter alia the electronic devices to be formed on the templates which are to be created on the substrate, and may also depend on the material of the III-nitride. In a step e) growth of a first III-nitride material is performed or at least initiated. Step e) indicates the initial growth, in the form of substantially pyramidal seeds 105, protruding from the holes 104. In a subsequent step f), which need not be included in all embodiments, as will be explained, the seeds 105 are grown into nanowires 106, by continued growth of the III-nitride material of the seeds 105, e.g. by CVD or VPE in a nanowire growth step, wherein a nitrogen source flow and a metal-organic source flow are present. In an embodiment including growth of nanowires as in step f), the process from d) to f) is typically continuous.

In one embodiment, the seed 105 and subsequently grown nanowires 106 comprise GaN. By growth from holes 104, which represent a very small portion of the substrate surface, a large majority of any dislocations in the substrate III-nitride 102 are filtered out. In addition, dislocations close to the edge of a hole 104 tend to bend off towards one side of the grown nanowire 106. Nanowires of GaN are thus grown,

11

normally in a hexagonal shape with 6 equivalent and smooth m-plane facets, where dislocations are seen to terminate towards the  $SiN_x$  mask. The result is entirely or substantially dislocation free seeds 105 or nanowires 106 of GaN, e.g. to a degree of at least 90% or at least 99% of the seeds 105 or nanowires 106 being dislocation free.

5

10

15

20

25

30

A nitride semiconductor nanowire 106 as discussed herein is in this context defined as an essentially rod-shaped structure with a diameter less than 1 micron, such as 50-100 nm and a length up to several µm. The method of growing nitride semiconductor nanowires according to one non-limiting embodiment of the invention utilizes a CVD based selective area growth technique. A nitrogen source and a metalorganic source are present during the nanowire growth step and at least the nitrogen source flow rate is continuous during the nanowire growth step. The V/III-ratio utilized for nanowire growth is significantly lower than the V/III-ratios commonly associated with the growth of nitride based semiconductor, as also outlined in the referenced earlier US application.

For an embodiment of GaN, processing according to g) of Fig. 1 may continue. Here, a GaN volume element 107 is grown on each nanowire 106. This step of forming the volume element 107 on the nanowires 106 may be carried out by CVD or VPE in a volume element growth step, wherein the nitrogen source flow and the metal-organic source flow are present. Preferably, the molar V/III-ratio during the volume element 107 growth step is higher than the molar V/III-ratio during the nanowire growth step. The volume element 107 grows to comprise a discreet insulating or semi-insulating GaN pyramid formed around each GaN nanowire 106.

In an alternative embodiment, processing according to step g) of Fig. 1 may be performed from the seed stage of e), without fully growing nanowires 106, as indicated by the vertical arrow in the drawing between steps e) and g). Also this step of growing a GaN volume element 107 on seeds 105 may be carried out by CVD or VPE in a volume element growth step, wherein the nitrogen source flow and the metal-organic source flow are present. Preferably, the molar V/III-ratio during the volume element 107 growth step is higher than the molar V/III-ratio during the seed growth step. The volume element 107 grows to comprises a discrete insulating or semi-insulating GaN pyramid formed around each GaN seed 105. Further details related to volume growth may also be obtained e.g. from the referenced US application by the instant inventor.

12

The process also includes a planarizing step. This may be carried out either after a nanowire growth step f), or alternatively after a volume element 107 growth step g), as indicated in Fig. 1.

5

10

15

20

25

30

In one embodiment, in which a GaN growth of nanowires 106, and potentially also a GaN volume element 107, is subjected to planarizing to obtain a flat c-plane mesa as shown in h), the inventors have discovered the surprising effect that, by carefully selecting process parameters, the planarization can be performed without, or at least without any significant, desorption of GaN. In such an embodiment, the planarization is instead obtained by controlled atomic redistribution of the nanostructure, i.e. the nanowire 106 when planarizing from f) to h), or the volume element 107 when planarizing from g) to h). Such a step may be carried out by providing a high, or even very high, flow of Nitrogen-containing material, typically NH<sub>3</sub>, while throttling, or preferably completely omitting, supply of additional flow of Ga source material. In other words, no or substantially no new Ga atoms are supplied. In one embodiment, the flow of NH<sub>3</sub> may e.g. be in the order of 5-20, in certain embodiments within 9-10 slm, while the Ga source is completely shut off. The process temperature may be maintained as held in a receding volume growth step, or be elevated, e.g. in the range of 1000-1200 degrees Celsius for GaN (the range going down to 700 for InGaN growth and up to 1500 for AlGaN growth). The inventors have found that the research results indicate that by selecting suitable process conditions, Ga atoms may break their crystal bond, without actually being completely desorbed and leave the GaN crystal surface. Instead, single Ga atoms may still be physically attached, even if the chemical bond is broken, herein referred to as physisorbed. Such a physisorbed Ga atom may travel on the surface of the GaN device, and reattach at another place. More specifically, given the right conditions, such as exemplified, a cone of a volume growth or element 107 may grow in the normal direction to the slanting s-plane, such that vertical m-planes underneath, and the planar top c-plane, increase. By providing the high NH<sub>3</sub> flow, or back pressure, while the temperature is optimally elevated, sufficient mobility of physisorbed Ga atoms is obtained, while excessive dissociation is avoided, such that the described atomic redistribution may be obtained. The process temperature at the planarizing step should preferably still be kept below a certain upper level, for the purpose of avoiding a three phase system where liquid Ga mayform dropplets on the surface of the GaN device.

5

10

15

20

25

30

13

Exemplary test results are depicted in Fig. 2, where Fig. 2A shows a substantially cone-shaped or pyramidal GaN device as created by volume growth 107. Fig. 2B illustrates the transformation of a device of Fig. 2A, when subjected to planarization by atomic redistribution, as described. Evidently, the m-planes and the c-plane have increased, while the s-plane has decreased. The result is, inter alia, that an enlarged cplane has been obtained, usable for providing e.g. epitaxial layers or other provision of contacts etc. Still, the decreased or even eliminated degree of dislocations in the GaN surface as obtained by mask growth, is maintained. In other words, the average amount of dislocations per surface area unit is substantially lower, ideally nil, as compared to an epitaxially grown continuous GaN surface, such as layer 102. Furthermore, the increase of the c-plane in the planarization step can be obtained in situ, without removal of the substrate from the machine after nanowire and potential volume growth, and without involvement of other material, such as etchants. This way, process speed and reliability may be improved. Test results have also shown that in one embodiments, atomic reconstruction may be carried out under circumstances such that mobile physisorbed Ga atoms will rather attach on the m-plane than on the c-plane. In such an embodiment, the results of the in crystal reconstruction involves the effect that a wider c-plane may be, which is usable for component configuration, than for a pure etching or polishing process.

In one embodiment, the suggested process is applied for an InGaN device. In such a process, steps a) to d) are also included. In one variant, the substrate layer 102 may also include an InGaN layer, on which a seed 105 and subsequently a nanowire 106 is grown of InGaN. Volume growth of InGaN is then carried out, on the InGaN nanowire 106, in step g). In an alternative embodiment, which has provided more reliable lab results, the process from a) to e) is the same as for GaN, i.e. with GaN seed growth on a GaN substrate layer 102. However, the GaN growth is stopped at the seed stage, preferably when the seed 105 is only a small pyramid, preferably with no m-plane over the mask level. After that, volume growth of InGaN is applied onto the GaN seed 105, to the state of a pyramid volume as in g). By starting with GaN growth, a lower level of dislocations may potentially be provided in the seed 105. In addition, by providing volume growth of InGaN already on the small seed 105 of GaN, rather than on a GaN nanowire, the risk for dislocation errors in the volume growth is minimized.

14

In the planarizing step from g) to h) of an InGaN volume 107 at an elevated temperature, a high degree of dissociation is normally involved, and may be dominating over any atomic redistribution. Fig. 3A illustrates an InGaN volume device 107, and although this is only a top view, its pyramidal shape is evident. Fig. 3B shows such volume device after planarizing, e.g. at a temperature in the range of 1100-1200 degrees Celsius, with a high NH<sub>3</sub> flow of 5-10 slm and absent any additional provision of In or Ga during the planarizing step. Also in this case, the planarization is obtained without providing any etchants, and c-plane increase is also obtained without any minimization of the width of the devices. As can be seen, though, a pattern of trenches may occur in the c-plane surface, potentially caused by the different boiling temperature of In and Ga. In a preferred embodiment, a repair step of providing additional InGaN growth may therefore be carried out, after planarization. When doing so, pyramidal growth will again occur, as during the preceding volume growth step from e) to g).

5

10

15

20

25

30

However, only a limited number of atomic layers are required, and after that, further epitaxial growth may be carried out to form electrical components, e.g. red and green light-emitting diodes. Fig. 3C shows a slanted image of such a device 300, where the planarized InGaN body 308 forms the base part, additional InGaN repair layers 309 are provided thereon, and epitaxial component layers 310 are formed on the repair layers 309.

Also Fig. 4 illustrates the process of manufacturing a light emitting diode on an InGaN device as described with reference to the preceding description and drawings, starting from a GaN seed. In the middle lower picture of Fig. 4, the side view of device 300 also clearly shows the layers 308, 309, and 310.

In one embodiment, the general growth process incorporating planarization is employed for the production of AlGaN devices. One such device 500 is shown in a side cross-section view in Fig. 5. The high degree of reactivity of Al with other materials presents a hurdle for growing AlGaN from mask holes, since the Al may grow on the mask too. For this reason, the inventors have come up with a new way of manufacturing planar AlGaN templates, on which to provide further epitaxial growth for component production. Referring back to Fig. 1, the process steps from a) to f) are carried out with GaN, for the beneficial reasons already referred to with regard to elimination or minimization of dislocations. (The process may alternatively be halted already at the seed level of e), dependent inter alia on hole size and on how large GaN planar mesas

15

are desired.) After a plurality of GaN nanowires 106 (or seeds 105) have been grown to contain desired volume, a planarizing step is carried out at h). In other words, there is preferably no volume step g) involved in the AlGaN process.

The result after atomic distribution as described above for GaN, will be a flat mesa 508 with a relatively small diameter, e.g. compared to the hole, since there is much less material in the growth when no volume growth step has been carried out. As an example, for a mask hole 104 size of 60-100 nm, the planarized GaN mesa structure 508 may have a width of 200-300 nm, i.e. in the range of only e.g. 2-5 times the mask hole size. In addition, the flat GaN structure will be configured, by atomic redistribution, to be very thin, e.g. with a GaN thickness t1 in the range of 30-100 nm.

5

10

15

20

25

30

In a subsequent process step, AlGaN growth is begun. As noted, layers may then grow on all parts of the substrate and on all facets of the flat GaN mesas. More importantly, AlGaN growth is deliberately continued until a layer 509 having a relatively large thickness t2, compared to t1. The reason for this is that any plastic deformation, as caused by the gitter mismatch between GaN and AlGaN, will occur in the GaN layer 508 rather than in the AlGaN layer 509. So, rather than a thin AlGaN layer 509 stretching to adapt to the crystal structure of the GaN mesa layer 508, a relatively thick AlGaN layer 509 will compress or contract the GaN layer 508, in the region of the interface between the materials. The growth of AlGaN layer 509 shall preferably be carried out at a comparatively low temperature, for AlGaN growth, which will help retain template shape at subsequent higher temperatures when adding layers over layer 509. The result is a substantially or entirely dislocation free AlGaN layer, on which further epitaxial layers 510, contacts or other component structures may be built.

In various embodiments, incorporating any one of the above-referenced embodiments and materials, the process may involve epitaxially growing a semiconductor displacing layer on the planarized volume element such that an upper surface of the displacing layer is located above the upper tip of the nanowire or seed, and the upper surface of the displacing layer forms the upper surface of each of the base elements, or alternatively that planarizing is halted at a stage where said tip is still below the upper c-plane layer of the planarized device.

Referring back to Fig. 1, in one aspect of the invention, a planarizing step is carried out to reform and merge or unite adjacent nanowire of volume growths. This is schematically illustrated through step i) of Fig. 1. This may be carried out either after a

16

nanowire growth step f) or after a volume element 107 growth step g), and can be seen as a continued planarizing step via stage h). The result is a continuous planar semiconductor layer or film 109, obtained from a plurality of separate growths. This process is referred to herein as coalescing.

5

10

15

20

25

30

As an example, a planar GaN layer may be obtained by coalescing. In one embodiment, GaN nanowire growth may be obtained using standard precursors TMG, TEG, NH3 and nitrogen and hydrogen carrier gases, on a patterned substrate, with a thin mask layer 103 – silicon nitride, silicon dioxide or similar. Openings 104 in the mask can be done by the standard lithographic techniques like nanoimprint or electron beam lithography, and developed using dry etching techniques like ICP-RIE and wet chemical etching. The spacing between the openings 104 can be adjusted during nanoimprint or EBL – typical values are 400, 600, 1000 or 2000nm. The opening diameter is defined in the nanoimprint or EBL lithographic process, with typical values between 50-400nm, depending on the used lithography technology. By means of suitable process steps, e.g. as described with reference to steps a) to e) above, a GaN seed 105 may be grown. Dependent on selected process parameters, the seed may evolve to nanowires 106 as in step f) or to volume elements 107 as in step g). Alternatively, the volume elements 10/ may be created by radial volume growth on nanowires 106 grown in step f).

In one embodiment volume GaN growth or GaN nanowires are subjected to a coalescing/planarization step, in which a cohesive c-plane planar layer is obtained as shown in Fig. 1 i). In such an embodiment, the coalescing step may be carried out under a nitrogen-sustaining background condition using, for example, ammonia, while throttling or completely omitting column-III element-containing gas precursor as described above with reference to Fig. 1.

Fig. 6A shows volume growth structures as described in steps a-g.

The semiconductor structure having a plurality of individual volume growths (or nanowires) may be subjected to a subsequent coalescing step for merging the individual structures. The coalescing step may e.g. involve processing of the substrate at a temperature in the range of 1000-1200 degrees Celsius, with a high NH3 flow of 1-10 slm and absent any additional provision of Ga.

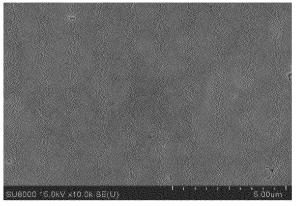

Fig. 6B shows a flat c-plane GaN surface after the coalescing step, in which it is observable that the individual growth structures flatten out and coalesce together. Fig. 6C shows a zoom out overview of larger area with uniformly coalesced GaN planar

17

film. In the drawn figure above Figs 6B and C, it is indicated that the reformation has progressed such that the top of each nanowire is exposed to the planar coalesced surface. It should be noted, though, that in other embodiments planarization may be obtained by reformation only of the volume growth, such that a seed or nanowire grown prior to, and encapsulated by, the volume growth is not exposed.

5

10

15

20

25

30

A variant of the embodiment described with reference to Figs 6A-B may be to continue volume growth as shown in Fig. 6A until the individual growths merge to some degree, at least at the base close to the mask surface. In such an embodiment, the subsequent coalescing step will nevertheless cause reformation of the grown structures, so as to form a cohesive flat surface extending over the individual growth positions.

For individual growths from a patterned mask 103, the orientation of the nanowires or volume growths can be such that the side facets can be oriented in any of two in-plane orientations, i.e. in [1-100] or [-12-10]. While it would seem that merging of individual adjacent nanowires or volume growths would benefit from such adjacent growths having facing facets, the inventors have found that the flat c-plane GaN surface after the coalescing step can be formed in any of those two orientations. For example, in the planar semiconductor structure obtained in Fig. 6B, the originating nanowires are facing in [-12-1-0] with respect to each. The reformation process with mobile physisorbed atoms is consequently a suitable process for producing a cohesive planar semiconductor III-Nitride layer or film 109.

In one embodiment, a planar III-N film 110 can further be grown on the coalesced film 109. An example is shown in Fig. 6D by means of a SEM top view of a 500nm thick planar GaN layer 110 that has been grown on the coalesced film 109, while Fig. 6E shows a cross-section SEM image of the structure.

In accordance with one aspect, the inventors have found out that by controlling the coalescing step growth conditions it was possible to grow a coalesced planar layer from groups of two or more structures to form a larger platelet or mesa, e.g. compared to single structure mesas as in Fig. 2B. An example of such a structure is shown in Fig. 7A, which shows a triplet structure consisting of three volume growth structures, which have been coalesced into one planar platelet 701. Fig 7B shows a variant, where five growths have been merged into one planar platelet 703. The ability to, in this way, form separate planar layers, designed in shape and size, gives the opportunity not only to fabricate wafers with separate insulated devices but also to provide the wafer with pre-

18

deployed vias already at the wafer fabrication step. In one embodiment, a substrate may e.g. be configured with a mask 103 having a predetermined pattern of openings 104, distributed such that growth through the openings and subsequent coalescing will result in a desired shape of a planar semiconductor structure. In such embodiments, the volume GaN growth or GaN nanowires could be subjected to a radial volume enlargement growth step in order to make the decrease the gaps in between neighbouring nanowires or volume growth structures, but it is not necessary to for the purpose of obtaining the flat c-plane GaN surface.

5

10

15

20

25

30

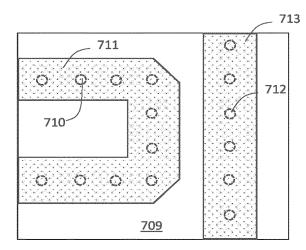

Fig. 7C illustrates, by way of a schematic example, a part of a substrate 709 provided with a mask having openings. In this embodiment, the openings are provided in an ordered manner, such that a first subset 710 of the openings form one pattern, and a second subset 712 of the openings form another pattern. After growth of semiconductor structures through the openings, e.g. in accordance with the preceding description, nanowires and/or volume elements will extend from the substrate surface through the openings 710, 712. In a step of coalescing, preferably carried out in situ in the same machine as used for growing and without intermediate removal of the substrate, the grown structures are subjected to operating conditions in which atoms are mobilized but kept attached, physisorbed, at the surface of the respective growth. In selected suitable conditions, as exemplified above for the steps of reformation and coalescing, the individual growths will flatten out, and closely adjacent growths will merge into a common planar layer. By arranging the openings in a manner such that certain growths will merge and certain will not, planar layers 711, 713 that are cohesive but also separate from each other may be formed. Such planar layers 711 and 713 may also assume a large variety of sizes and shapes. This provides a freedom of production that has hitherto not been available in the art of preparing planar III-N structures.

The coalescing step, as described brings a non-obvious advantage over, traditional, epitaxial methods of re-growth, such as ELO (Epitaxial -lateral overgrowth). Epitaxial regrowth is made under active growth-conditions with supersaturation as driving force. Crystallization from the gas phase reduces the free energy of the system, resulting in forced conditions where dislocations and defects can be formed, especially when non- aligned crystal growth fronts meet and coalesce, as in epitaxial regrowth and epitaxial overgrowth. In contrast, the reformation occurring during e coalescing step is carried out near thermal equilibrium.

During the planarization and coalescing step as described herein, no, or little additional column-III element is added to the epitaxial crystal. The epitaxial system is in a zero net-volume growth state but with conditions allowing for high surface mobility of physisorbed material. When dissociation- and chemisorption-rates are kept comparable, each physisorbed molecule is, ideally, free to repeatedly move, chemisorb and dissociate until it finds the lowest-energy crystal position to occupy. Dislocations in the crystal structure, as well as most defects results in a higher free energy, whereas the total binding energy to the crystal will be lower than in the case of the ideal crystal. All in all, making the planarization and coalescing step is much less prone to produce or comprise such crystal faults.

In one embodiment, the volume III-nitride growth is carried out with In or Al to obtain a flat c-plane InGaN or AlGaN surface. As a more specific example, a coalescing process applied for InGaN growth is described. In such a process steps a to d are included. Depending on step d array design coalesced planar InGaN layer or coalesced InGaN structure consisting of groups of two or more nanowires or volume growth structures could be grown, e.g. through steps e-g or e-f-g. By supplying In-precursor flow simultaneously with Ga-precursor flow during volume-growth ternary InGaN may be formed in step g) from e) or f). When the volume growth is subjected to the coalescing step i), both gallium and indium atoms are free to move, chemisorb and dissociate until they find low energy crystal positions. A planar InGaN coalesced layer is thus formed.

An exemplary InGaN coalesced layer is given in Fig. 8A, in which a cohesive InGaN layer made from a plurality of merged individual growths of InGaN can be seen. In a preferred embodiment a repair planar InGaN growth can be carried out after the coalescing step, as described above with reference to Fig. 4. When doing so a planar InGaN growth will occur, on top of the coalesced layer. Since it is typically difficult to avoid defect formation and material degradation with higher indium, the method proposed herein provides an alternative growth technique where crystal faults are less prone to form. A planar InGaN layer, obtained by the proposed coalescing method, with reduced dislocation density will provide a very good substrate for optoelectronic device applications. It could be also directly used in typical CVD or VPE growth of III-nitride optoelectronic devices.

Fig. 8B shows an alternative embodiment of volume III-nitride growth with In or Al, developed to obtain a flat c-plane InGaN or AlGaN surface formed from a group of three openings in SiNx mask. The structure of Fig. 8B is similar to the structure of Fig. 7A, in that a limited number (three in this example) of ordered growths are coalesced into a via. The structure of Fig. 8B has not, yet, been provided with a repair layer, as evidenced by the surface structure which is characteristic for a transformed InGaN structure. In order to obtain the structure of Fig. 8B, a mask structure as shown in d) is selected, where the number, order and spacing of openings 104 are carefully selected. In step e) groups of two or more nanowires or volume growth structures could be formed. By introducing additional indium precursor flow during volume growth indium content in the volume growth g) can be added. When the volume growth is subjected to a coalescing step i) nanostructures or volume growth are coalesced, i.e. merged and made to form an increased c-plane surface. In one preferred embodiment, a smoothening InGaN growth layer can be grown out after the coalescing step, in a surface repair step.

The embodiments of Figs 7A and B and 8B illustrate examples of a semiconductor structure comprising a substrate, a mask provided on a surface of the substrate, the mask having a plurality of openings provided in an ordered manner along the substrate surface, wherein a cohesive planar via of a III-N material extends over a plurality of openings in a substrate mask. The planar via is formed by merged individual semiconductor structures grown through different openings. The openings may be provided at equidistant positions along a path along the substrate surface. The coalescing step may be carried out in situ in a subsequent step to individual semiconductor growth, wherein atomic reformation is carried out at an increased temperature with a high back pressure of nitrogen, without or with substantially no additional source of column III semiconductor material.

The solutions outlined above, for providing flat structures of III-N semiconductor material, such as e.g. GaN and InGaN, in the form of platelets or even coherent flat layers is a great and also unexpected achievement. It is now 100 years since the so-called Czochralski process was invented, according to which a solid crystal is slowly pulled up from a melt. This is still the basis for growth of Si ingots. Other, similar, techniques used for fabrication of conventional semiconductors, such as Ge, GaAs, GaP and InP, are the Bridgman technique and the float zone process. These technologies all have in common the use of a liquid/solid growth front, with a minutely controlled

growth rate and temperature gradient,  $\Delta T$ , and initiated from a dislocation-free crystal seed. In these growth processes,  $\Delta T$  will determine the growth rate, with a high  $\Delta T$  forcing fast condensation of the crystal. In the Czochralski process the "Perfect Si Crystal" conditions are met when the growth rate is sufficiently fast as to avoid creation of Si crystal vacancies, but sufficiently slow, or unforced as to avoid incorporation of interstitial Si. In Czochralski growth, a low  $\Delta T$  gives a low driving force for precipitation and the system is said to be close to thermodynamic equilibrium. In thermodynamic equilibrium, the atoms have the same probability for precipitation into the crystal from the liquid phase as for dissociation from the crystal phase to the liquid. In this case other factors will determine where the atoms go in the end. It is easy to realize that interstitial incorporation of atoms, or inclusions of vacancies represent a smaller decrease in free energy for the system than incorporation of adatoms at their respective lattice sites.

With reference to Fig. 9A, the Czochralski process is a transition between liquid phase and the crystal phase, represented by the double-headed arrow. However, as seen from the diagram, a phase boundary between solid and liquid GaN emerges only at pressures above 6 GPa. This makes liquid phase epitaxy of GaN an immense challenge with GaN semiconductor wafers instead predominantly fabricated on foreign substrates, by metal organic vapor phase epitaxy (MOVPE). In order to improve the crystal quality of GaN grown on sapphire and Si, epitaxial lateral overgrowth (ELO) has been developed in order to reduce dislocation density and provide higher quality substrates, andf early results did show much promise and lately it has been adopted for nanowires.

In various embodiments of the solutions proposed herein, though, the epitaxial physics of a peculiar epitaxial regime is explored, which is denoted crystal reformation herein. This crystal reformation may be carried out as a step of planarization of a III-nitride material grown on a seed at a mask opening, as outlined for several different embodiments above. The planarization of the III-nitride material serves to form a plurality of discrete base elements having a substantially planar upper surface. Crystal reformation is performed near equilibrium conditions and supersaturation is not created by addition of material. In contrast to MOCVD growth in general, it's not required to supply the III-V nitride crystal growth front with column III-material in order to drive the phase transition. One significant aspect of equilibrium growth and the described method is reversibility of the phase transition, i.e. the ability to reverse the propagation

22

of the growth front, going forwards or backwards, by changing the thermal bias. In our case the thermal bias, driving the reformation, is supplied by the difference in surface energy of the crystal facets: Net atomic dissociation at one crystal facet takes place simultaneously with net precipitation, or crystallization, at another facet. In this sense the epitaxial growth front comprises all involved facets but local growth rates may be both positive or negative.

5

10

15

20

25

30

In various embodiments, a supply of NH<sub>3</sub> is kept in order to avoid degradation of the crystal surface, and the temperature is elevated, as exemplified for various embodiments. In yet another embodiment for GaN, the elevated temperature may be in the range of 900 °C and 1200 °C, or between 700 °C and 1000 °C. In one embodiment the elevated temperature is above the sublimation temperature of the crystal material. During the reformation, the inventors have observed the surprising effect that a substantial portion of the crystal is transferred from one facet to another.

Fig. 9B illustrates a calculated Ga–N phase diagram at atmospheric pressure. Here it may be noted that the Gas + GaN regime, where the reformation step would be positioned, marked by dashed lines, requires an excess of atomic nitrogen and that Ga would be in liquid form. Furthermore, Fig. 9C shows the known Ga–N binary phase diagram according to Subvolume F 'Ga-Gd – Hf-Zr' of Volume 5 'Phase Equilibria, Crystallographic and Thermodynamic Data of Binary Alloys' of Landolt-Börnstein - Group IV Physical Chemistry. As noted therein, "An experimentally determined phase diagram is not available". This goes to show that hitherto there is in fact not sufficient experimental data to draw the phase-diagram for N > 50%, The phase diagram corresponding to the reformation-conditions is not available. Although the environmental condition suggest Ga to be in liquid phase, as the data suggest an additional condition of a low desorption –rate of the Ga atoms within the process window. The solutions proposed herein, for providing planar III-N materials by reformation, consequently form a new solution with beneficial, unexpected results, obtained by processes carried out in an untrodden territory of physics.

The shape-transformation is most likely driven by the surface energies of the facets. Growth on higher order facets are favored, such that formation of lower order facets and the 0001 c-plane is strongly favored, as can be anticipated from published work on kinetic Wulff crystal shapes in GaN. The kinetic Wulff model aims to predict the shape of a small crystal based on the relative surface energy ratios of the facets. The

23

inventors propose to complement this model with an atomic picture, which may be associated with the embodiments described herein:

1. Each atom that dissociates from the crystal may stay in a physisorbed state or desorb to the gas-phase. Since the volume of the crystal remains intact, it may be concluded that desorption can be discounted and the atoms remain physisorbed until they are incorporated to the crystal again.

5

10

15

20

25

30

- 2. The probabilities for going into a physisorbed state and into a crystal-bound state are both high, but with a higher incorporation probability at the side facets and a higher desorption probability at the top facet (since the crystal height decreases). With high sticking and dissociation probabilities the atoms may alter freely between physisorbed states and crystal bound states. Formation of dislocations, point-defects, vacancies and interstitials usually results in a weaker bonding to the crystal and smaller decrease in free energy of the system than the positioning on a "perfect lattice site". Since the atoms can move freely between crystal-bound states, the atoms will typically end up at the positions with higher binding energy, and there will thus be a barrier to form a defect or dislocation, as compared to bonding at a "perfect site".

- 3. The physisorbed atoms are preferably column-III atoms, most common species being Gallium, Indium, and Aluminium. The natural state for these materials at the conditions used is liquid form (Room pressure melting T: Ga 30°C; In 157°C; Al 660°C, all having boiling Ts above 2000°C). Their vapor pressures are all low, below 1pascal at 1000°C, explaining the low loss of material through evaporation, although some evaporation-loss will be expected.

- 4. The physisorbed column III atoms can have rather high diffusion rates and diffusion lengths on the order of 1µm for Ga and 10µm for In. A good physical description is the physisorbed atoms forming a two-dimensional cloud on the surface which will retain a constant concentration within the limits of diffusion lengths which in various embodiment is larger than the dimensions of the template structures. The cloud is supplied by dissociation of column III atoms from the crystal lattice and the reformation rate will be given by the relative differences in atomic dissociation rate and sticking rate to the respective facets. As long as the reformation-rate is sufficient low for the surface-diffusive state of column-III material to retain a relatively constant, conformal concentration of column-III material and the dimensions of structure is of similar, or less, length than the diffusion-length, then the supply of III-material will not

24

be diffusion-limited but crystal incorporation is only governed by the activation energy of the crystal binding. This is what usually is referred to equilibrium conditions.

5. In a preferred embodiment, the background flow of NH<sub>3</sub> will be sufficiently high when it provides a supply of nitrogen, e.g. through pyrolysis of NH<sub>3</sub>, which is sufficient to provide a reservoir of nitrogen for III-material atoms to combine with during the reformation, at which a substantially planar upper surface is formed on a template facet. Pure nitrogen, N2, is inert at the used temperatures but the moderate activation energy for pyrolysis of NH<sub>3</sub> supplies us with enough atomic nitrogen to allow us to work with a phase transition touching on the right end side of the diagram in figure 9C. However, nitrogen sources with even lower cracking temperatures would allow for reformation at lower temperatures and possibly better control over incorporation of crystal nitrogen vacancies.

5

10

15

20

25

30

As noted, the planar upper surface will be formed and increased by redistribution of column III material, e.g. Ga or In, caused by favored growth on other template facets. At such a supply level, the nitrogen supply will not be diffusion limited, thereby fulfilling the condition for equilibrium growth with regards to the column V-element. Increasing the flow above this level may inhibit surface diffusion of column-III material productive flow of NH<sub>3</sub>. It's more likely that atomic nitrogen supply is limited by low pyrolysis-rate of NH<sub>3</sub>. Therefore the reformation step can be a very good candidate for use of alternative nitrogen sources where more efficient pyrolysis can be achieved. There are several such sources, examples being hydrazine, methylated hydrazine, such as dimethyl hydrazine, tertiarybutylhydrazine, tertiarybutylamine and also nitrogen-plasma, although reactivity of nitrogen radicals could decrease diffusion lengths appreciably.

Although using a gas phase environment, crystal reformation stands in closer relation to the original liquid phase epitaxy methods that have been the centennial state of the art of high-purity bulk-grown semiconductor wafers. The thermodynamics involved also suggest that the conditions for reformation can be made uniquely preservative, allowing for minimal introduction of new dislocations during the coalescence. Being a new epitaxial regime, this will, as is the case for all new epitaxy methods, require further understanding of the physics involved in order to avoid introduction of new crystal defects. The approach, detailed herein, relies on a

25

combination of epitaxial growth, low temperature optical characterization and the implementation of a physical growth-model.

5

10

15

20

25

30

The nanostructures proposed herein are preferably all based on GaN nanowire seeds, or pyramidal seeds but other compositions of nitride material, including In and Ga can be used. The suggested embodiments are different, mainly due to specific challenges in context of materials and structures grown. Growing high Al composition AlGaN on GaN or high In-composition InGaN on GaN introduce crystal lattice mismatch, therefore the GaN seeds and templates are kept small in size to more easily accommodate strain without introducing new misfit dislocations. It may be even better but more challenging to incorporate In or Al, already during nanowire growth. Also, it may be preferable to use an AlGaN NW or grow and reform an AlGaN template directly. This is currently challenging due to the low diffusion-length of Al atoms but maybe preferably long term when such working conditions can be developed. With that said we should distinguish practical practical differences between GaN, InGaN nad AlGaN methodology from fundamental preferences. All embodiments described may work may work for any combination of nitride material, as ternary nitride NW growth and reformation are further developed.

A great advantage is the elimination of substrate dislocations through the nanowire or seed growth, giving fully dislocation—free platelets. This gives a second similarity to the Czochralski process, since it generates high quality crystals not only due to the well-controlled equilibrium-proximity, but also since it generates its own dislocation free seed.

The reformation of whole arrays of nanostructures, such as nanowire-based structures, provides additional structural advantages which will now be discussed.

Nanowire-based structures provide vertical m-planes, [10-10]. These planes provide surfaces for efficient lateral coalescence of material rearranged from the top of the nanowire structures. As previously outlined, it has been noted that physisorbed column III atoms may form a two-dimensional cloud on the surface, when the nanowire-based structure is subjected to an elevated temperature in a Nitrogen-rich environment as exemplified, which cloud will retain a constant concentration within the limits of diffusion lengths of the physisorbed atoms. This may result in reformation, at which a C plane, directed upwards from the nanowire structures, tends to increase while III-nitride material instead grows on the m-planes.

WO 2019/068919

5

10

15

20

25

30

26

PCT/EP2018/077233

In various embodiments the coalesced layer will thus be formed by formation of material in between the nanowire structures and, depending on process parameters such as temperature, and chosen length and spacing between the nanowire structures, the reformation will form a thin coalesced layer. More specifically, the reformation will cause growth between the nanowire structures adjacent upper portions of the nanowire structures. The result will be a coalesced layer which is thinner than the remaining length of the nanowire structures, leaving an appreciable lower part of the nanostructures un-coalesced. An example associated with this embodiment will now be described with reference to Figs 10 and 11.

Fig. 10 schematically illustrates method step of the production of a III-nitride semiconductor device, corresponding to the process described with reference to Fig. 1.

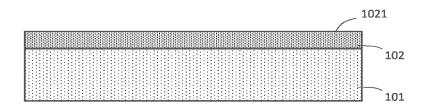

In Fig. 10A a base substrate 101 of e.g. sapphire is provided with one or more buffer layers 102 of e.g. GaN. Together, the layers 101 and 102 form a substrate, with a substrate surface 1021.

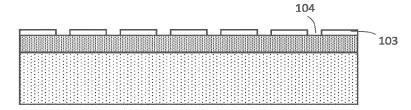

In Fig. 10B a mask layer 103 of e.g. SiNx has been formed on top of the substrate, which mask layer comprises apertures or holes 104. The holes may be very narrow, e.g. with a diameter of 50-200 nm, or e.g. 60-100 nm. The pitch between the holes 104 may e.g. be in the order of 200-2000 nm, e.g. 400-1000 nm, and is selected dependent on inter alia the electronic devices to be formed on the templates which are to be created on the substrate, and may also depend on the material of the III-nitride.

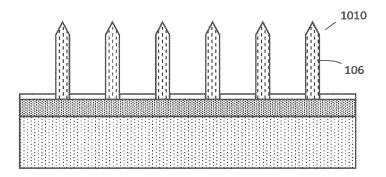

Fig. 10C illustrates how nanowires 106 have been grown on the substrate surface 1021 of the buffer layer 102 through the holes 104, e.g. by CVD or VPE in a nanowire growth step, wherein a nitrogen source flow and a metal-organic source flow are present. In one embodiment, the nanowires 106 comprise GaN.

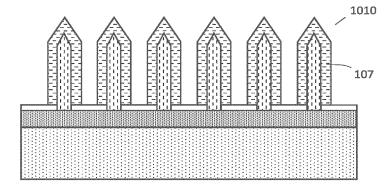

Fig. 10D illustrates the result of a volume growth step to provide a volume element, carried out after nanowire growth, as previously discussed herein. In the drawings, a different pattern is indicated for the nanowires 106 than the volume element 107, but is should be noted that this only serves the purpose of clearly showing the different elements. The nanowires 106 and the volume element 107 may be provided in the same material, or different materials, as previously outlined.

For the embodiment at hand, the volume growth step is optional, but may be advantageous. As a result of the processes ending at Fig. 10C or 10D, a nanowire structure 1010 is formed, which comprises a nanowire 106 and optionally a volume

27

element 107 provided onto the nanowire 106. It is a noted advantage that the nanowire structures are close to each other, with a pitch and width that results in a spacing between the nanowire structures which is substantially smaller than the length of the nanowire structures 1010. However, growing relatively narrow nanowires 106 will increase the positive effect of minimizing threading dislocations, which means that it may be more advantageous to provide a volume element 107 onto the nanowires 106 may be more beneficial than growing thicker nanowires 106. In one embodiment, the nanowire structures 1010 are grown to have a height which is at least 3 times a width of said spacing. In another embodiment, the nanowire structures are epitaxially grown to have a height which is at least 4, 5 or 6 times a width of said spacing.

5

10

15

20

25

30

Fig. 11 illustrates a coalesced device formed after a planarizing step, carried out on a device including nanowire structures 1010 as shown in e.g. Fig. 10C or Fig. 10D. By carrying out the step of reformation on extended nanowire structures 1010, with a suitably small distance between each other compared to the length of the nanowire structures 1010, coalescence will appear at an upper part 1012 of the nanowire structures 1010 to form a coherent planar layer 1020, having an upper first surface 1022, and a backside surface 1023. As noted, the growth of the layer 1020 is carried out at an elevated temperature in a nitrogen-rich environment without, or substantially without, providing further column III material. Instead, due to distinctive different surface energies of the crystal planes, column III atoms are released from primarily the top portions of the nanowire structures 1010, so as to form and increase a C plane. Under suitable process parameters, as exemplified, such released column III material will attain a physisorbed and will further crystallize with nitrogen atoms to form a column III-nitride layer 1016 on the vertical M planes. This reformation will subsequently lead to coalescing of the M planes of adjacent nanowire structures 1010 to form the coherent layer 1020. Due at least in part to the larger length of the nanowire structures 1010 than the distance between the nanowire structures 1010, as given by the pitch and width of the nanowire structures 1010, coalescence into a coherent layer 1020 will take place primarily or only at an upper part 1012 of the nanowire structures 1010. A lower part 1014 of the nanostructures may thus remain un-coalesced, and free of solid material, or at least not occupied by material redistributed by coalescence from the nanowire structures 1010. Since column III material grown 1016 on the M planes at

28

coalescence is taken from the top of the nanowire structures 1010, the resulting height of the nanowire structure is smaller after reformation.

5

10

15

20

25

30

The coalesced layer 1020 will hence be formed by formation of material in between the nanowire structures 1010 and forms a thin layer 1020. The depth of the coalescence 1016, which basically defines the thickness of the coalesced layer 1020, depends inter alia on chosen length of and spacing between the nanowire structures 1010. In various embodiments the coalesced layer 1020 may have a depth between 100nm and 500nm, but dependent on dimensions and process parameters this may be decreased to a range between 10 and 100 nm, leaving the lower part 1014 of the nanostructures un-coalesced. In various embodiments the coalesced portion 1016 may be in the range of half the resulting length of the nanowire structures 1010, such that the upper portion 1012 is between 20-70 % of the resulting length of the nanowire structures 1010 after coalescence.

As discussed earlier, the reformation method provides better conditions for formation of a continuous layer with low generation of dislocations at the coalescing interfaces. In addition, reformation allows a thinner continuous layer to be realized than the nanostructures being epitaxial overgrown, through ELO, since planarization through ELO must be achieved by adding material on pyramidal and lateral surfaces of the nanostructures. It's also easy to see that similar nanostructures grown without a nanowire, mainly terminated by pyramidal –s-planes and c-planes, lack the prolonged vertical m-plane facets, enabling efficient lateral reformation.

Fig. 12 shows an embodiment in which a subsequent layer 1030 is provided on top of the planarized and coalesced layer 1020. This layer 2013 may serve to provide a c-plane surface repair growth if required, or simply to provide thickening of the coalesced layer 1020. This step may be performed at a lower temperature than the planarizing step. In various embodiments, the surface repair growth may be performed by providing a supply of column III material, preferably the same column III material as in the planarized second III nitride material, and may result in additional layers of pyramidal growth. In preferred embodiment, the repair layer thus created may only include one or a few atom layers, such that there will be no substantial decrease of the planarized template surface. Further layers may be grown on top of a repair layer. Subsequent steps may include forming a device, such as an electronic component, in or

29

on the planarized and coalesced plurality of base elements, on top of the subsequent layer 1030, e.g. by further epitaxial growth.

5

10

15

20

25

30

Fig. 13A shows an embodiment provided by Flip-chip technology, in which the epitaxial stack is separated from the base substrate layer 101, while leaving layers from the growth-substrate 102, such as a GaN buffer layer. from the growth-substrate 102 the stack may also.

Fig. 13B shows another embodiment provided by Flip-chip technology, in which the epitaxial stack is entirely separated from the substrate 101, 102, and also the mask layer 103.

Fig. 14 illustrates a beneficial effect rendered by the embodiments described with reference particularly to Figs 10-13. As already noted, by growth from mask holes 104, which represent a very small portion of the substrate surface, a large majority of any dislocations, such as threading dislocations 1400 illustrated in the drawing, in the substrate III-nitride 102 are filtered out by means of the mask layer 103. In addition, it has been noted that threading dislocations close to the edge of a hole 104 tend to bend off towards one side of the grown nanowire 106, or to the side edge of the mask hole 104. An explanation for this may be that strain generated by threading dislocations in the grown material tend to be released by growth of the nanowires 106, since the material in the nanowire 106 is substantially free to relax in three dimensions, as compared to the III-nitride material in the planar grown buffer layer. Both a thicker mask layer and longer nanowires may therefore provide an advantageous suppression or elimination of threading dislocations. More particularly, coalescing the nanowire structures 1010 at only an upper part, leaving a lower part of the nanowire structures 1010 separated, further minimizes the risk for threading dislocations to appear in the resulting coalesced layer 1020, and hence in any further grown layers 1030. The embodiments outlined with reference to Figs 10-14 may be provided with features of production and structure according to any of the other embodiments outlined herein, unless contradictory. As an example, devices with two or more separate coalesced surfaces, as described with reference to Figs 7 and b, may also be generated by means of coalesced layers as indicated in Fig. 11.

Various embodiment of a device as shown in Figs 11-14 may be provided by means of a mask 103 of a spacing of e.g. 150-1000 nm, such as 700 nm, between mask holes 104 with an aperture of 50-300 nm, where larger apertures may be used with