US 20190165037A1

## (19) United States (12) Patent Application Publication (10) Pub. No.: US 2019/0165037 A1

### Chae et al.

#### (54) LED UNIT FOR DISPLAY AND DISPLAY APPARATUS HAVING THE SAME

- (71) Applicant: SEOUL VIOSYS CO., LTD., Ansan-si (KR)

- (72) Inventors: Jong Hyeon Chae, Ansan-si (KR); Seong Gyu Jang, Ansan-si (KR); Ho Joon Lee, Ansan-si (KR); Chang Yeon Kim, Ansan-si (KR); Chung Hoon Lee, Ansan-si (KR)

- (21)Appl. No.: 16/198,792

- (22) Filed: Nov. 22, 2018

#### **Related U.S. Application Data**

(60) Provisional application No. 62/590,870, filed on Nov. 27, 2017, provisional application No. 62/590,854, filed on Nov. 27, 2017, provisional application No. 62/594,769, filed on Dec. 5, 2017, provisional application No. 62/595,932, filed on Dec. 7, 2017, provisional application No. 62/608,297, filed on Dec. 20, 2017, provisional application No. 62/614,900, filed on Jan. 8, 2018, provisional application No. 62/635, 284, filed on Feb. 26, 2018, provisional application No. 62/683,564, filed on Jun. 11, 2018.

#### **Publication Classification**

(51) Int. Cl.

| H01L 27/15 | (2006.01) |

|------------|-----------|

| H01L 33/40 | (2006.01) |

### May 30, 2019 (43) **Pub. Date:**

| H01L 33/38 | (2006.01) |

|------------|-----------|

| H01L 33/42 | (2006.01) |

| H01L 33/50 | (2006.01) |

| H01L 33/10 | (2006.01) |

| H01L 25/13 | (2006.01) |

(52) U.S. Cl. CPC ...... H01L 27/156 (2013.01); H01L 33/405 (2013.01); H01L 33/38 (2013.01); H01L 25/13 (2013.01); H01L 33/507 (2013.01); H01L 33/10 (2013.01); H01L 33/42 (2013.01)

#### (57)ABSTRACT

A light emitting device including first, second, and third LED sub-units, and electrode pads disposed on the first LED sub-unit, electrically connected to the LED sub-units, and including a common electrode pad electrically connected to each of the LED sub-units, and first, second, and third electrode pads connected to a respective one of the LED sub-units, in which the common electrode pad, the second electrode pad, and the third electrode pad are electrically connected to the second LED sub-unit and the third LED sub-unit through holes that pass through the first LED sub-unit, the first, second, and third LED sub-units are configured to be independently driven, light generated in the first LED sub-unit emitted to the outside through the second and third LED sub-units, and light generated in the second LED sub-unit is emitted to the outside through the third LED sub-unit.

**FIG.** 1

**FIG. 2**

FIG. 3A

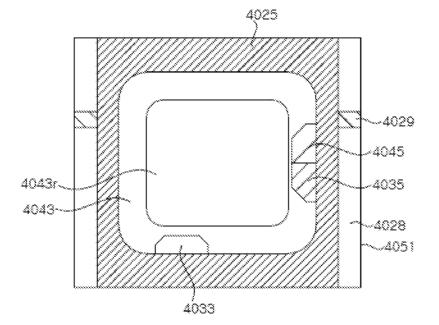

# FIG. 4A

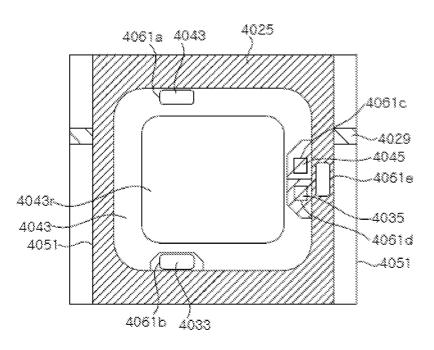

FIG. 4B

FIG. 5B

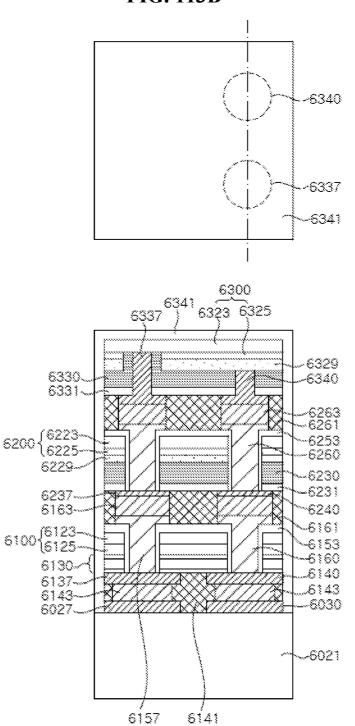

FIG. 6A

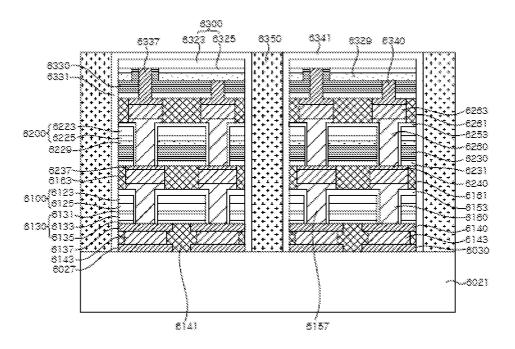

FIG. 8A

FIG. 8B

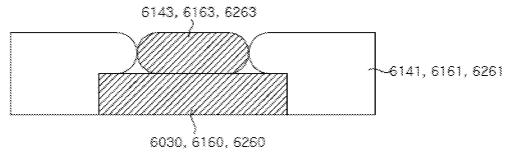

FIG. 9A

FIG. 9B

**FIG. 10A**

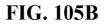

**FIG. 10B**

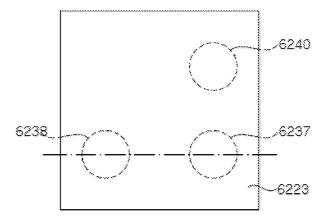

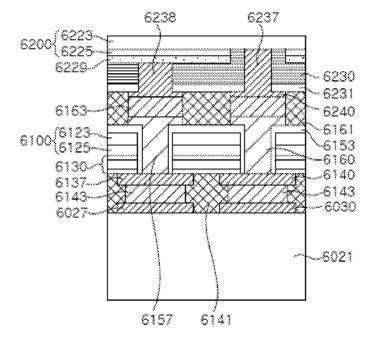

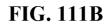

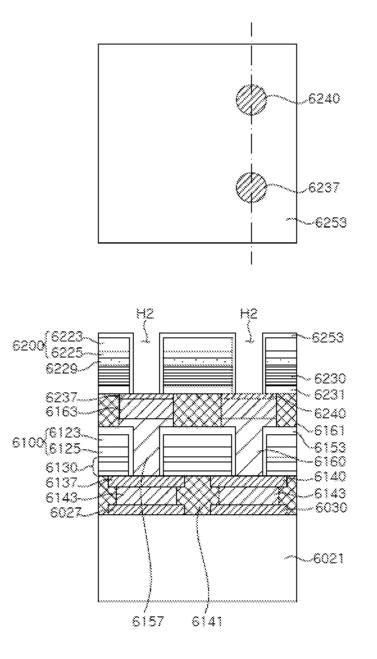

**FIG. 11B**

**FIG. 12B**

**FIG. 13A**

**FIG. 13B**

**FIG. 14A**

**FIG. 14B**

**FIG. 15A**

**FIG. 15B**

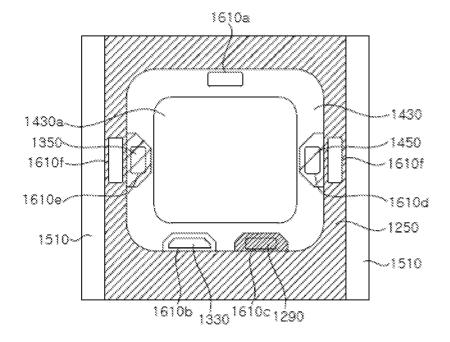

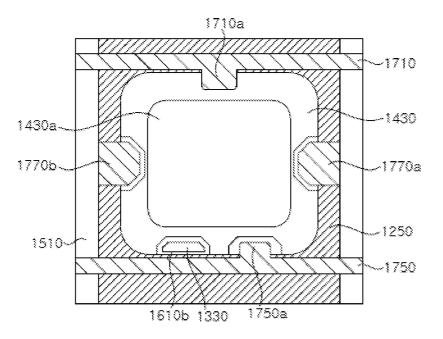

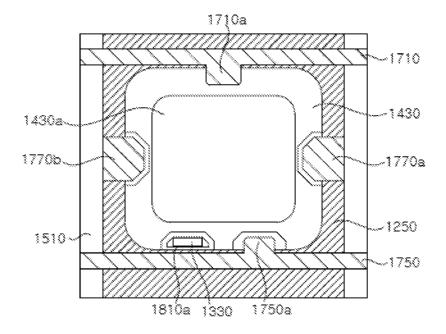

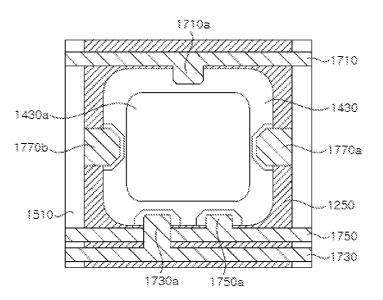

**FIG. 16A**

**FIG. 16B**

**FIG. 18**

**FIG. 21A**

FIG. 22

FIG. 23

FIG. 24

FIG. 25

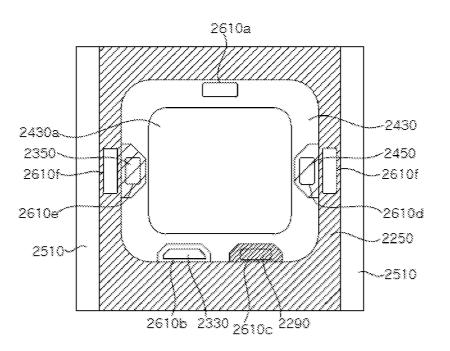

**FIG. 26A**

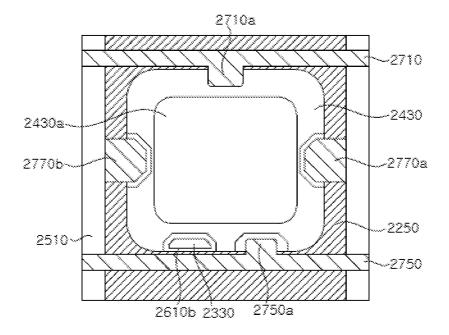

**FIG. 27B**

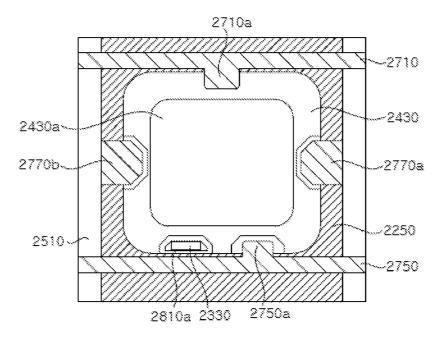

**FIG. 28A**

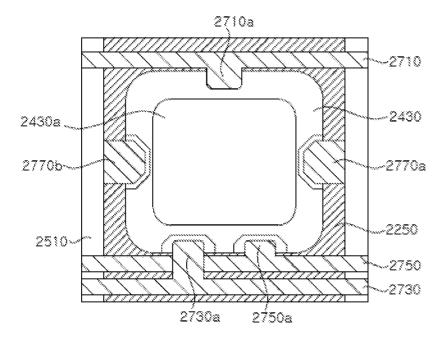

**FIG. 29**

**FIG. 30A**

**FIG. 30B**

**FIG. 31A**

**FIG. 31B**

**FIG. 32A**

FIG. 32B

**FIG. 33**A

**FIG. 33B**

**FIG. 34A**

**FIG. 35**A

**FIG. 35B**

FIG. 36

1000

**FIG. 37B**

**FIG. 37E**

FIG. 39

**FIG. 40**

**FIG. 41**

FIG. 42

**FIG. 43**A

**FIG. 43B**

**FIG. 43C**

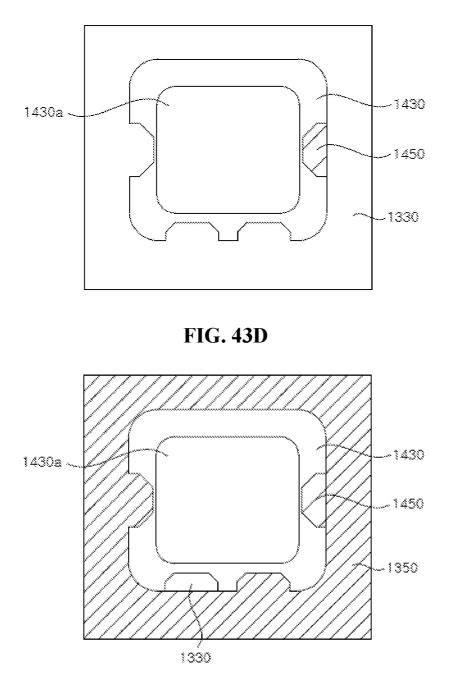

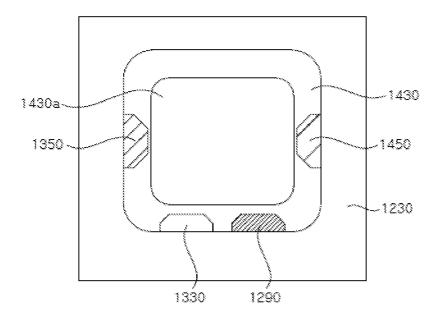

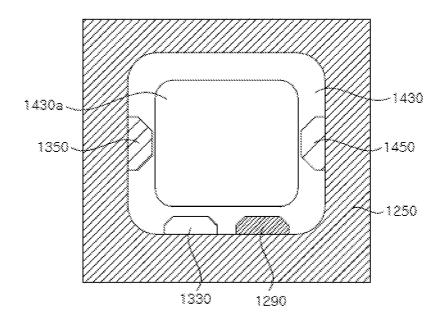

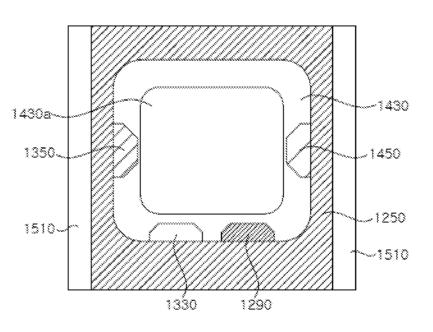

FIG. 43E

**FIG. 43**F

FIG. 43G

FIG. 43H

**FIG. 43J**

**FIG. 43K**

**FIG. 45**

**FIG. 46**

# **FIG. 47**A

#### FIG. 47B

## FIG. 47C

### **FIG. 47D**

**FIG. 47E**

## FIG. 48

FIG. 50

FIG. 51

FIG. 52

**FIG. 53B**

**FIG. 53**C

**FIG. 53D**

**FIG. 53E**

**FIG. 53**F

**FIG. 53G**

FIG. 53H

FIG. 53I

**FIG. 53K**

FIG. 54

2430a 2731b 2731b 2511 2511 2731a 2751a

**FIG. 55**

**FIG. 59A**

**FIG. 59B**

## **FIG. 60A**

**FIG. 60B**

#### **FIG. 60C**

**FIG. 60D**

**FIG. 61A**

**FIG. 61B**

**FIG. 62A**

**FIG. 63**A

FIG. 63B

#### **FIG. 64A**

FIG. 64B

**FIG. 65A**

FIG. 65B

**FIG. 66A**

FIG. 66B

**FIG. 67A**

#### **FIG. 68A**

**FIG. 68B**

**FIG. 71A**

**FIG. 71B**

4000

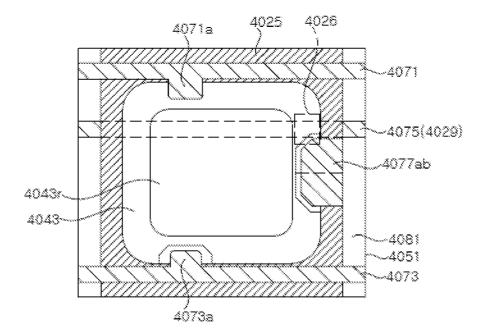

**FIG. 73A**

**FIG. 73B**

**FIG. 73F**

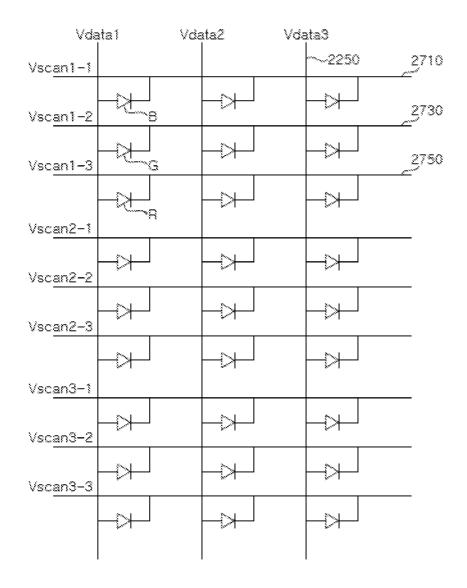

| Vde              | ita i | Vdata2 | Vdata3 |      |

|------------------|-------|--------|--------|------|

| Vsc <u>an1-1</u> |       |        | ~-4025 | 4071 |

| Vsc <u>an1-2</u> |       |        |        | 4073 |

| Vsc <u>an1-3</u> | - Age |        |        | 4075 |

| Vscan2-1         |       |        |        |      |

| Vscan2-2         |       |        |        |      |

| Vscan2-3         |       |        |        |      |

| Vscan3-1         |       |        |        |      |

| Vscan3-2         |       |        |        |      |

| Vsc <u>an3-3</u> |       |        |        |      |

|                  |       |        |        |      |

|                  |       |        |        |      |

**FIG. 74**

**FIG. 75**

**FIG. 76**

**FIG. 77**

**FIG. 78**

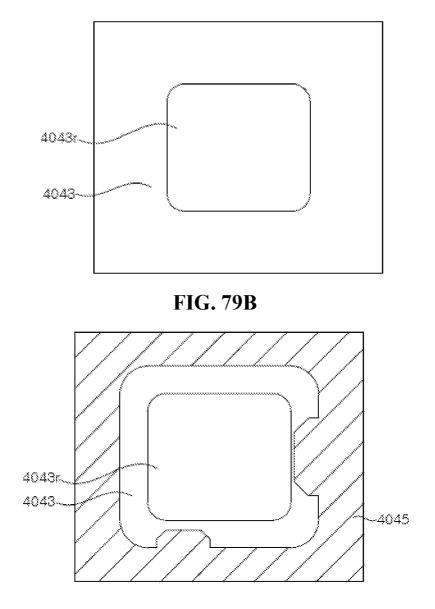

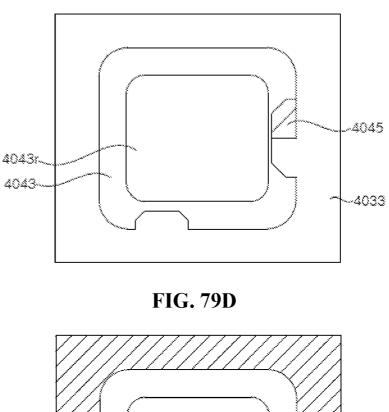

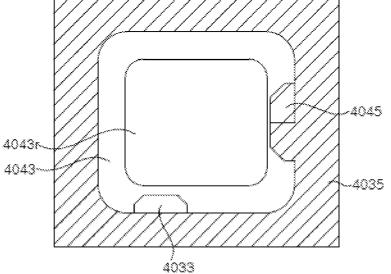

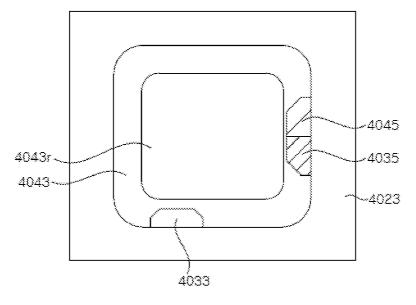

**FIG. 79A**

FIG. 79C

**FIG. 79E**

**FIG. 79F**

**FIG. 79G**

FIG. 79H

**FIG. 81A**

**FIG. 82**

**FIG. 84**

FIG. 86

**FIG. 87**

**FIG. 89**

**FIG. 90A**

**FIG. 90B**

**FIG. 91A**

FIG. 91B

FIG. 93B

**FIG. 95A**

FIG. 95B

FIG. 96

**FIG. 97B**

**FIG. 99A**

**FIG. 99B**

**FIG. 100**

FIG. 101B

#### FIG. 103A

FIG. 103B

**FIG. 104**

FIG. 106

FIG. 107A

# FIG. 108B

## FIG. 108C

### FIG. 108D

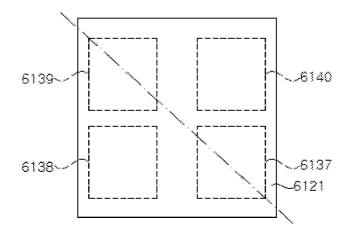

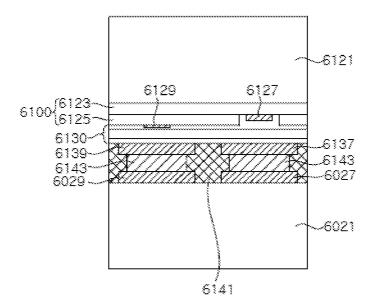

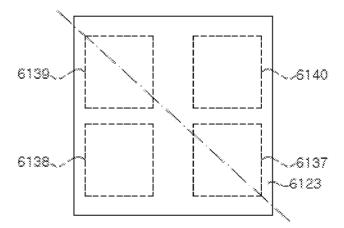

FIG. 109A

# FIG. 109C

#### FIG. 109D

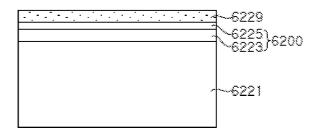

### FIG. 110A

# FIG. 110C

# FIG. 110D

**FIG. 111A**

**FIG. 111C**

FIG. 111D

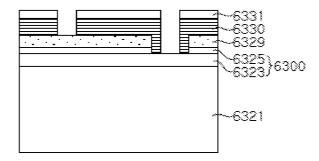

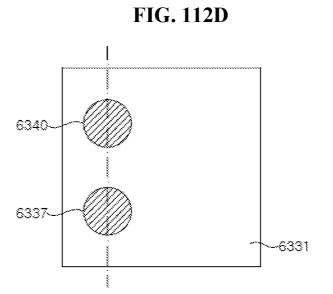

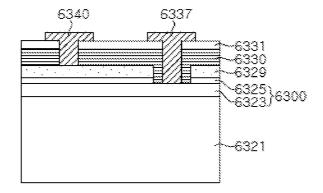

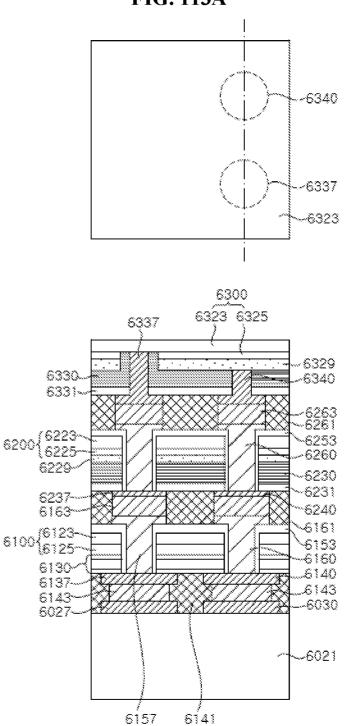

### FIG. 112C

**FIG. 113A**

FIG. 113B

**FIG. 114**

FIG. 115A

### FIG. 115B

Patent Application Publication May 30, 2019 Sheet 124 of 124 US 2019/0165037 A1

## FIG. 115C

#### LED UNIT FOR DISPLAY AND DISPLAY APPARATUS HAVING THE SAME

#### CROSS REFERENCES TO RELATED APPLICATIONS

**[0001]** This application claims priority from and the benefit of United States Provisional Patent Application No. 62/590,870, filed on Nov. 27, 2017, U.S. Provisional Patent Application No. 62/590,854, filed on Nov. 27, 2017, U.S. Provisional Patent Application No. 62/594,769, filed on Dec. 5, 2017, U.S. Provisional Patent Application No. 62/595,932, filed on Dec. 7, 2017, U.S. Provisional Patent Application No. 62/608,297, filed on Dec. 20, 2017, United States Provisional Patent Application No. 62/635,284, filed on Feb. 26, 2018, and U.S. Provisional Patent Application No. 62/683,564, filed on Jun. 11, 2018, the disclosures of which are hereby incorporated by reference for all purposes as if fully set forth herein.

#### BACKGROUND

#### Field

**[0002]** Exemplary implementations of the invention relate generally to a display apparatus and, more particularly, to a display apparatus having a light emitting diode (LED) unit pixel, a light emitting device for a display and a display apparatus, and to a light emitting device for a display with stacked structure of a plurality of LEDs and a display apparatus having the same.

#### Discussion of the Background

**[0003]** A light emitting diode has been used as an inorganic light source in various fields such as display apparatuses, automotive lamps, and general lighting. With advantages of long lifespan, low power consumption, and high response speed, the light emitting diode has been rapidly replacing a conventional light source.

**[0004]** Meanwhile, a light emitting diode of the related art has been mainly used as a backlight light source in a display apparatus. However, a micro LED display has been recently developed as a next-generation display that directly implements an image using the light emitting diode.

[0005] In general, the display apparatus implements various colors by using mixed colors of blue, green, and red. The display apparatus includes a plurality of pixels to implement an image with various colors, and each of pixels includes sub-pixels of blue, green, and red. The color of a specific pixel is determined by the color of the sub-pixels, and the image is implemented by the combination of these pixels. [0006] In the case of a micro LED display, the micro LEDs corresponding to each sub-pixel are arranged on a twodimensional plane. Therefore, a large number of micro LEDs are required to be disposed on one substrate. However, the micro LED has a very small size having a surface area of 10,000 square m or less, and thus, there are various problems due to this small size. Particularly, it is difficult to handle a light emitting diode having a small size, and it is not easy to mount the light emitting diode on a display panel, especially over hundreds of thousands or millions, and to replace a defective LED of mounted micro LEDs with a good LED.

**[0007]** In addition, since sub-pixels are arranged on a two-dimensional plane, the area occupied by one pixel including the sub-pixels of blue, green, and red is relatively increased. Therefore, in order to arrange the sub-pixels within a limited area, it is required to reduce the area of each sub-pixel, thereby causing deterioration in brightness through reduction in luminous area.

**[0008]** The above information disclosed in this Background section is only for understanding of the background of the inventive concepts, and, therefore, it may contain information that does not constitute prior art.

#### SUMMARY

**[0009]** Light emitting diodes constructed according to the principles and some exemplary implementations of the invention and displays using the same are capable of increasing a light emitting area of each sub-pixel without increasing the pixel area.

**[0010]** Light emitting diodes and display using the light emitting diodes, e.g., micro LEDs, constructed according to the principles and some exemplary implementations of the invention provide high reliability due to a stable LED structure and simplified manufacturing process in which a single via may be connected to one or more of semiconductor layers of each of the LED stacks.

**[0011]** Light emitting diodes and display using the light emitting diodes, e.g., micro LEDs, constructed according to the principles and some exemplary implementations of the invention provide pixels that can be simultaneously manufactured to obviate the cumbersome process of individually mounting the pixels.

**[0012]** Light emitting diodes and display using the light emitting diodes, e.g., micro LEDs, constructed according to the principles and some exemplary implementations of the invention are capable of being driven in an active matrix manner.

**[0013]** Light emitting diodes and display using the light emitting diodes, e.g., micro LEDs, constructed according to the principles and some exemplary implementations of the invention are capable of shortening a mounting process time.

**[0014]** Light emitting diodes and display using the light emitting diodes, e.g., micro LEDs, constructed according to the principles and some exemplary implementations of the invention are capable of preventing light interference between LED stacks by arranging first, second, and third LED stacks one over another to emit light with decreasing wavelengths of light. For example, the first, second, and third LED stacks may emit red light, green light, and blue light, respectively.

**[0015]** Light emitting diodes and display using the light emitting diodes, e.g., micro LEDs, constructed according to the principles and some exemplary implementations of the invention are capable of suppressing generation of secondary light between the LED stacks without arrangement of the color filters therebetween, which are generally formed between the LED stacks to prevent generation of secondary light by light emitted from adjacent LED stacks.

**[0016]** Additional features of the inventive concepts will be set forth in the description which follows, and in part will be apparent from the description, or may be learned by practice of the inventive concepts.

**[0017]** A display apparatus according to an exemplary embodiment includes a thin film transistor (TFT) substrate,

a first LED sub-unit disposed on the TFT substrate, a second LED sub-unit disposed on the first LED sub-unit, a third LED sub-unit disposed on the second LED sub-unit, electrode pads disposed between the TFT substrate and the first LED sub-unit, and connectors connecting the first, second, and third LED sub-units to a respective one of the electrode pads, in which the first LED sub-unit, the second LED sub-unit, and the third LED sub-unit are configured to be independently driven, light generated from the first LED sub-unit is configured to be emitted to the outside of the display apparatus by passing through the second LED subunit and the third LED sub-unit, and light generated from the second LED sub-unit is configured to be emitted to the outside of the display apparatus by passing through the third LED sub-unit.

**[0018]** The first, second, and third LED sub-units may include a first LED stack, a second LED stack, and a third LED stack, respectively, and the first, second, and third LED stacks may be configured to emit red light, green light, and blue light, respectively.

**[0019]** The display apparatus may include a first reflective electrode disposed between the TFT substrate and the first LED sub-unit and in contact with a lower surface of the first LED sub-unit, in which the connectors may include a first lower connector connecting the first reflective electrode to a first one of the electrode pads.

**[0020]** The connectors may further include a first upper connector connecting an upper surface of the first LED sub-unit to a second one of the electrode pads.

[0021] The display apparatus may further include a second transparent electrode interposed between the first LED subunit and the second LED sub-unit and in ohmic contact with a lower surface of the second LED sub-unit, and a third transparent electrode interposed between the second LED sub-unit and the third LED sub-unit and in ohmic contact with a lower surface of the third LED sub-unit, in which the connectors may further include a second lower connector connecting the second transparent electrode to the first one of the electrode pads, a second upper connector connecting an upper surface of the second LED sub-unit to a third one of the electrode pads, a third lower connector connecting the third transparent electrode to the first one of the electrode pads, and a third upper connector connecting an upper surface of the third LED sub-unit to a fourth one of the electrode pads.

**[0022]** The first lower connector may be connected to an upper surface of the first reflective electrode, the second lower connector may be connected to an upper surface of the second transparent electrode, and the third lower connector may be connected to an upper surface of the third transparent electrode.

**[0023]** The first upper connector may be connected to the upper surface of the first LED sub-unit, the second upper connector may be connected to the upper surface of the second LED sub-unit, the third upper connector may be connected to the upper surface of the third LED sub-unit, and at least one the upper connectors may be substantially annular in shape.

**[0024]** The connectors may further include intermediate connectors connecting the second upper connector and the third upper connector to the third one and the fourth one of the electrode pads, respectively.

**[0025]** Each of the connectors may pass through at least one of the first, second, and third LED sub-units.

**[0026]** The first lower connector, the second lower connector, and the third lower connector may be connected to the first one of the electrode pads, and the first upper connector, the second upper connector, and the third upper connector may be connected to different ones of the electrode pads, respectively.

**[0027]** The first lower connector, the second lower connector, and the third lower connector may be stacked over each other in a vertical direction, and the first upper connector, the second upper connector, and the third upper connector may be spaced apart from each other in the vertical direction and in a lateral direction.

[0028] The display apparatus may further include a second transparent electrode interposed between the first LED subunit and the second LED sub-unit and in ohmic contact with a lower surface of the second LED sub-unit, and a third transparent electrode interposed between the second LED sub-unit and the third LED sub-unit and in ohmic contact with a lower surface of the third LED sub-unit, in which the connectors may further include a second lower connector connecting the second transparent electrode to a third one of the electrode pads, a second upper connector connecting an upper surface of the second LED sub-unit to the second one of the electrode pads, a third lower connector connecting the third transparent electrode to a fourth one of the electrode pads, and a third upper connector connecting an upper surface of the third LED sub-unit to the second one of the electrode pads, and the first lower connector, the second lower connector, and the third lower connector may be separated from each other and are connected to the first, third, and fourth ones of the electrode pads, respectively, and the first upper connector, the second upper connector, and the third upper connector may be electrically connected to the second one of the electrode pads.

**[0029]** The first lower connector, the second lower connector, and the third lower connector may be spaced apart from each other in a vertical direction and in a lateral direction, and the first upper connector, the second upper connector, and the third upper connector may be stacked in the vertical direction.

**[0030]** The display apparatus may further include a first color filter interposed between the first LED sub-unit and the second LED sub-unit, and configured to transmit light generated from the first LED sub-unit and reflect light generated from the second LED sub-unit, and a second color filter interposed between the second LED sub-unit and the third LED sub-unit, and configured to transmit light generated from the first and second LED sub-units and reflect light generated from the first and second LED sub-unit light generated from the first and second LED sub-units and reflect light generated from the first and second LED sub-units.

**[0031]** The display apparatus may further include a first bonding layer interposed between the TFT substrate and the first LED sub-unit, a second bonding layer interposed between the first LED sub-unit and the second LED subunit, and a third bonding layer interposed between the second LED sub-unit and the third LED sub-unit, in which the second bonding layer is configured to transmit light generated from the first LED sub-unit, and the third bonding layer is configured to transmit light generated from the first and second LED sub-units.

**[0032]** The display apparatus may be configured to be driven in an active matrix manner.

**[0033]** The third lower connector and the third upper connector may be exposed by the third LED sub-unit in plan view.

**[0034]** The first reflective electrode may be disposed between the first LED sub-unit and the electrode pads.

**[0035]** The first, second and third LED subunits may include a micro LED having a surface area less than about 10,000 square m.

**[0036]** The first LED sub-unit may be configured to emit one of red, green, and blue light, the second LED sub-unit may be configured to emit a different one of red, green, and blue light from the first LED sub-unit, and the third LED sub-unit may be configured to emit a different one of red, green, and blue light from the first and second LED subunits.

[0037] A light emitting device according to an exemplary embodiment includes a first LED sub-unit, a second LED sub-unit disposed adjacent to the first LED sub-unit, a third LED sub-unit disposed adjacent to the second LED sub-unit, and electrode pads disposed on the first LED sub-unit and electrically connected to the first, second, and third LED sub-units, the electrode pads including a common electrode pad electrically connected to each of the first, second, and third LED sub-units, and first, second, and third electrode pads connected to a respective one of the first, second, and third LED sub-units, in which the common electrode pad, the second electrode pad, and the third electrode pad are electrically connected to the second LED sub-unit and the third LED sub-unit through holes that pass through the first LED sub-unit, the first LED sub-unit, the second LED sub-unit, and the third LED sub-unit are configured to be independently driven, light generated in the first LED subunit is configured to be emitted to the outside of the light emitting device through the second LED sub-unit and the third LED sub-unit, and light generated in the second LED sub-unit is configured to be emitted to the outside of the light emitting device through the third LED sub-unit.

**[0038]** The first, second, and third LED sub-units may include a first LED stack, a second, LED stack, and a third LED stack, respectively, and the first, second, and third LED stacks may be configured to emit red light, green light, and blue light, respectively.

**[0039]** The light emitting device may further include a first reflective electrode disposed between the electrode pads and the first LED sub-unit and in ohmic contact with the first LED sub-unit, in which the common electrode pad is connected to the first reflective electrode.

**[0040]** The first reflective electrode may include an ohmic contact layer in ohmic contact with an upper surface of the first LED sub-unit and a reflective layer that covers the ohmic contact layer.

**[0041]** The first reflective electrode may have a hollow portion defined by a substantially annular-shaped member, and the common electrode pad may pass through the hollow portion of the substantially annular-shaped member.

**[0042]** The light emitting device may further include a second transparent electrode interposed between the second LED sub-unit and the third LED sub-unit and in ohmic contact with a lower surface of the second LED sub-unit, and a third transparent electrode in ohmic contact with an upper surface of the third LED sub-unit, in which the common electrode pad may be electrically connected to the second transparent electrode and the third transparent electrode.

**[0043]** The common electrode pad may be connected to an upper surface of the second transparent electrode and an upper surface of the third transparent electrode.

**[0044]** Each of the first LED sub-unit and the third LED sub-unit may include a first conductivity type semiconductor layer and a second conductivity type semiconductor layer disposed on a partial region of the first conductivity type semiconductor layer, and the first electrode pad and the third electrode pad may be electrically connected to the first conductivity type semiconductor layer of the first LED sub-unit and the third LED sub-unit, respectively.

**[0045]** The light emitting device may further include a first ohmic electrode disposed on the first conductivity type semiconductor layer of the first LED sub-unit, in which the first electrode pad is connected to the first ohmic electrode.

**[0046]** The third electrode pad may be directly connected to the first conductivity type semiconductor layer of the third LED sub-unit.

**[0047]** The light emitting device may further include a first color filter disposed between the third transparent electrode and the second LED sub-unit, and a second color filter disposed between the first and second LED sub-units.

[0048] The first color filter and the second color filter may include insulating layers having different refractive indices.[0049] The common electrode pad and the third electrode pad may be electrically connected to the third LED sub-unit

through holes that pass through the second LED sub-unit. [0050] The light emitting device may further include a

substrate on which the third LED sub-unit is disposed.

**[0051]** The substrate may include a sapphire substrate or a gallium nitride substrate.

**[0052]** The light emitting device may further include an insulating layer disposed between the first LED sub-unit and the electrode pads, in which the electrode pads are electrically connected to the first, second, and third LED sub-units through the insulating layer.

**[0053]** The insulating layer may include at least one of a distributed Bragg reflector and a light blocking material.

**[0054]** A display apparatus may include a circuit board, and a plurality of light emitting devices arranged on the circuit board, at least some of the light emitting devices may include the light emitting device according to an exemplary embodiment, in which the electrode pads may be electrically connected to the circuit board.

**[0055]** Each of the light emitting devices may include a substrate coupled to the third LED sub-unit, and the substrates of the light emitting devices may be spaced apart from each other.

**[0056]** A light emitting device according to an exemplary embodiment includes a substrate, a first LED sub-unit disposed on the substrate, a second LED sub-unit disposed on the first LED sub-unit, a third LED sub-unit disposed on the second LED sub-unit, and electrode pads electrically connected to the first, second, and third LED sub-units, the electrode pads including a common electrode pad electrically connected to each of the first, second, and third LED sub-units by a single through-hole via, and first, second, and third electrode pads connected to a respective one of the first, second, and third LED sub-units.

**[0057]** The electrode pads may be disposed between the substrate and the first LED sub-unit, the through-hole via may include a plurality of connectors connected to each of the first, second, and third LED sub-units, and the connectors may include a first portion having a width greater than a width of the through-hole via.

**[0058]** The first LED sub-unit may include a reflective electrode disposed on a lower surface thereof, and the reflective electrode may contact the first portion of the corresponding connector.

**[0059]** The first, second, and third LED sub-units may be disposed between the electrode pads and the substrate, and the through-hole via may have a width that narrows in a direction from the electrode pads to the substrate.

**[0060]** The third LED sub-unit may include a reflective electrode disposed on an upper surface thereof, and the common electrode pad may directly contact the reflective electrode.

**[0061]** It is to be understood that both the foregoing general description and the following detailed description are exemplary and explanatory and are intended to provide further explanation of the invention as claimed.

#### BRIEF DESCRIPTION OF THE DRAWINGS

**[0062]** The accompanying drawings, which are included to provide a further understanding of the invention and are incorporated in and constitute a part of this specification, illustrate exemplary embodiments of the invention, and together with the description serve to explain the inventive concepts.

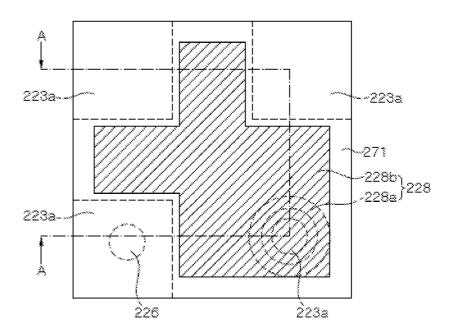

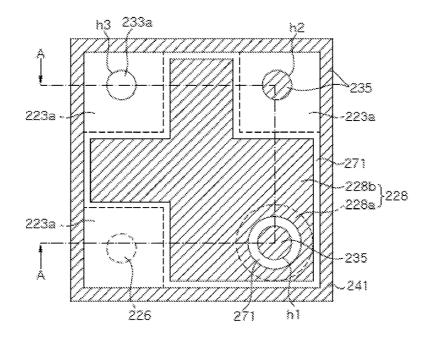

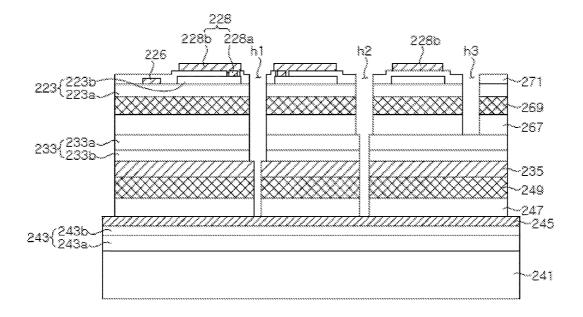

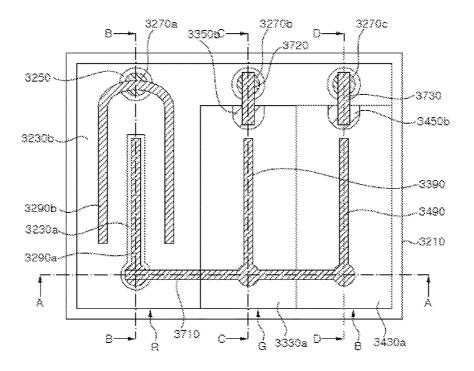

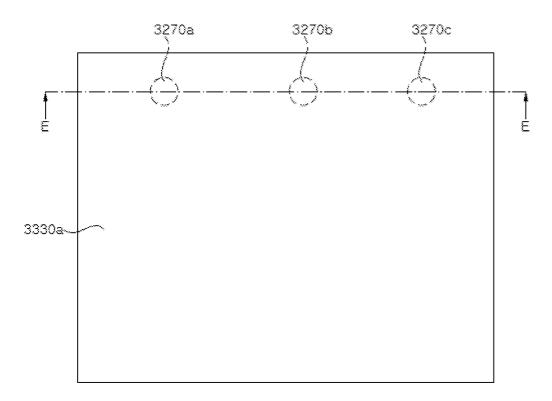

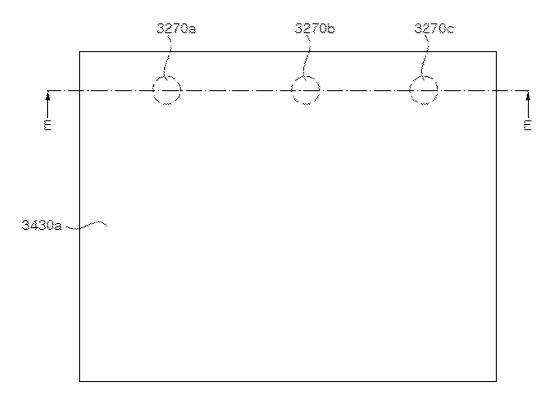

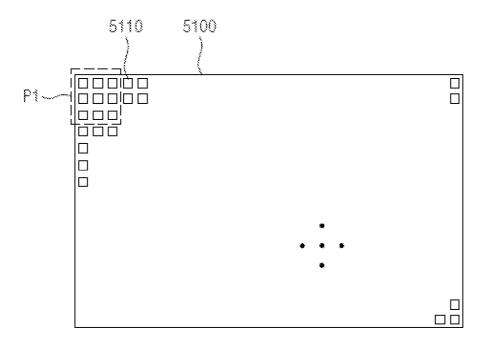

**[0063]** FIG. **1** is a schematic plan view of a display apparatus according to an exemplary embodiment.

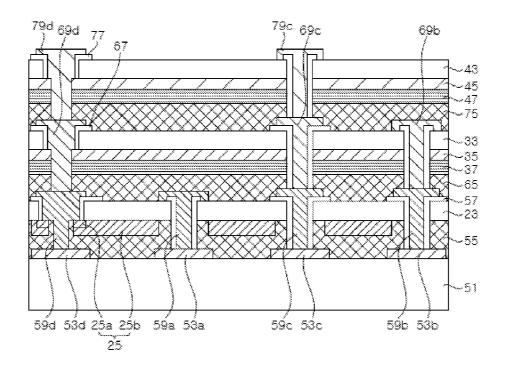

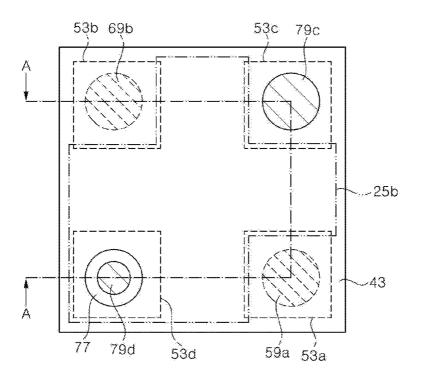

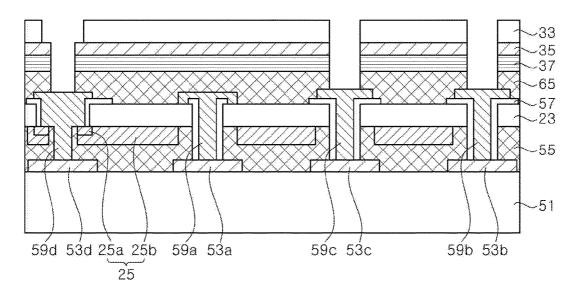

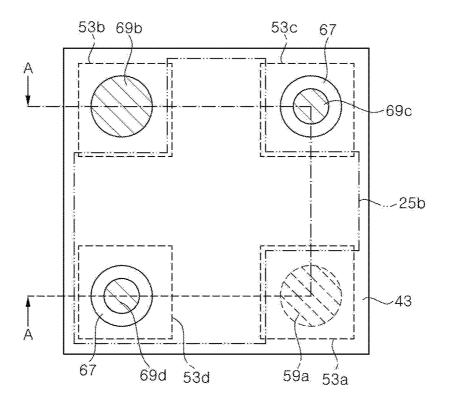

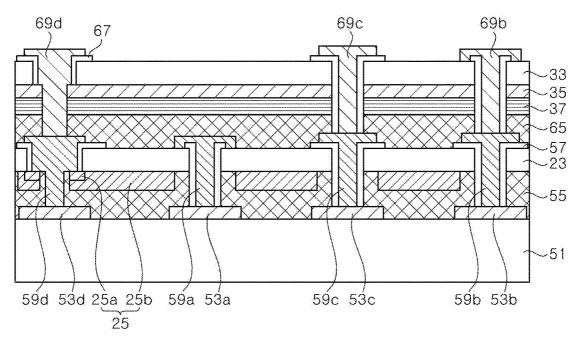

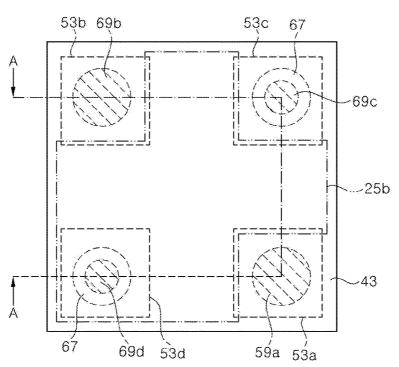

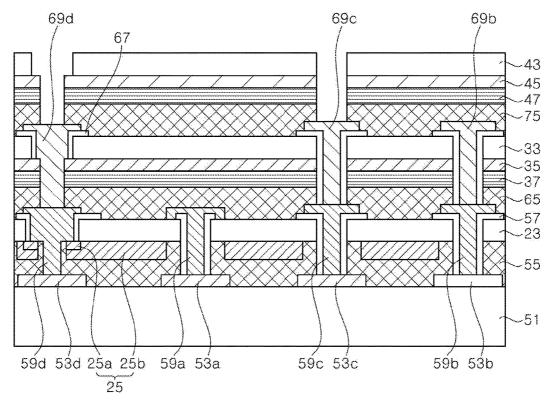

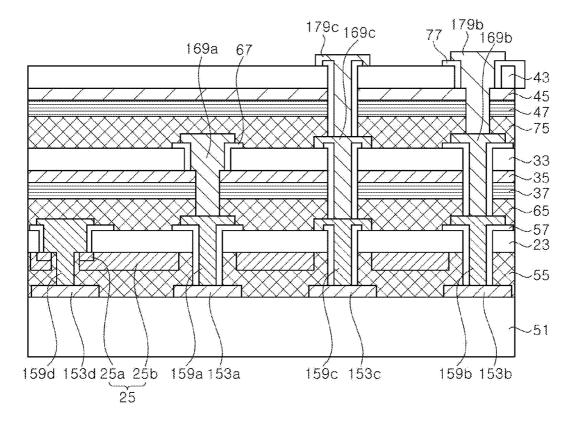

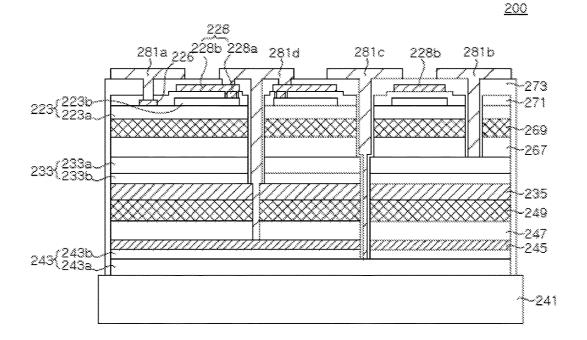

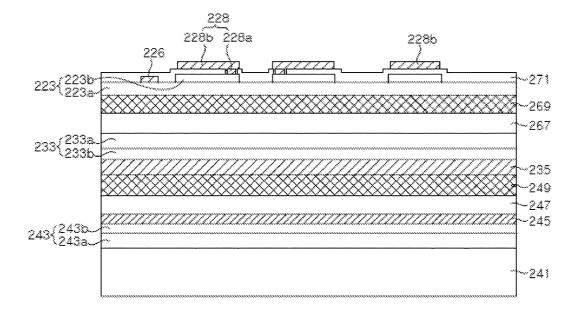

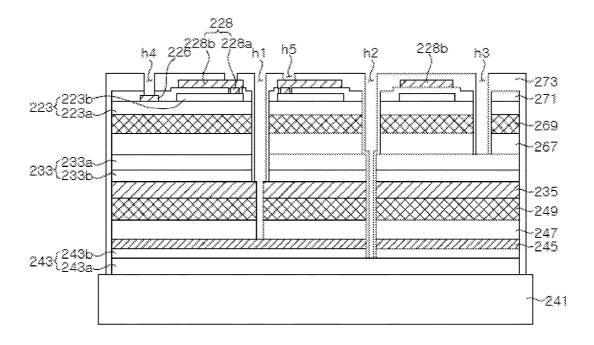

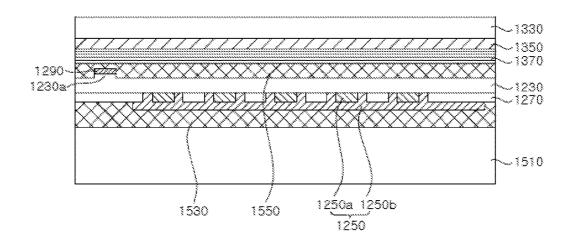

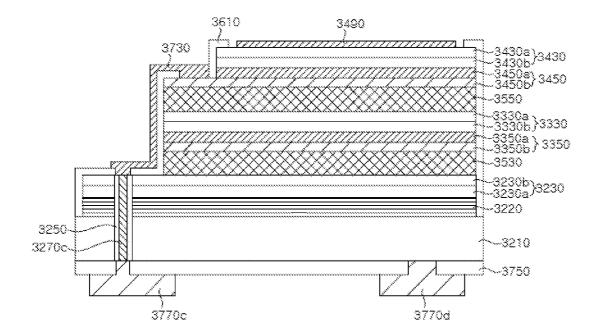

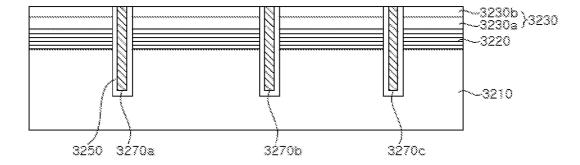

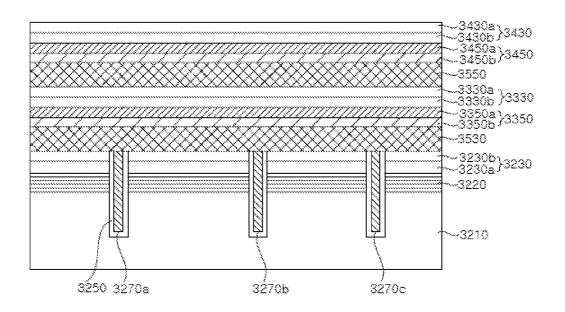

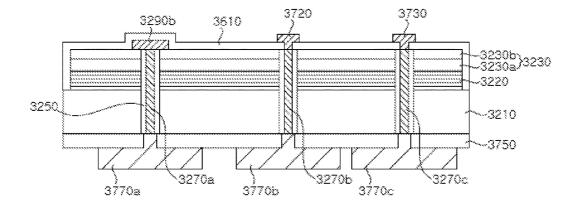

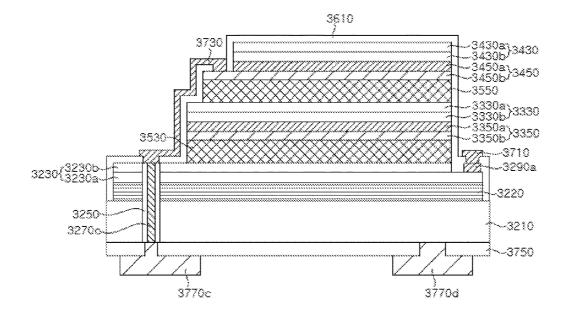

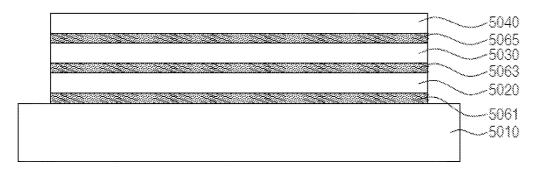

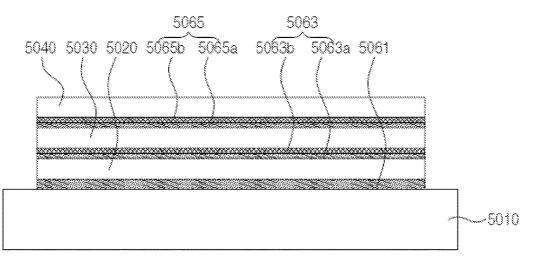

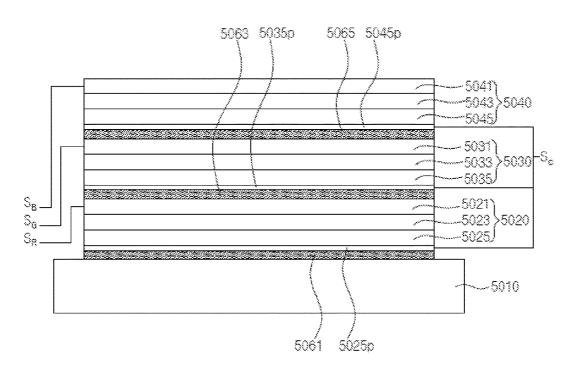

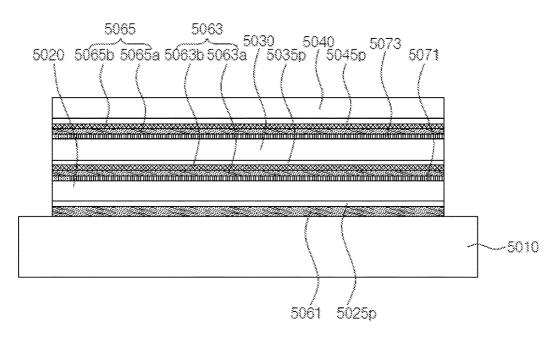

[0064] FIG. 2 is a schematic cross-sectional view taken along line A-A of FIG. 1.

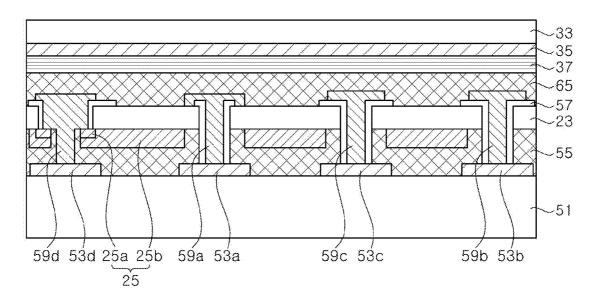

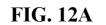

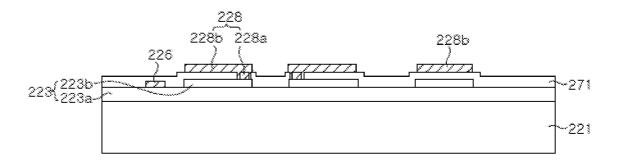

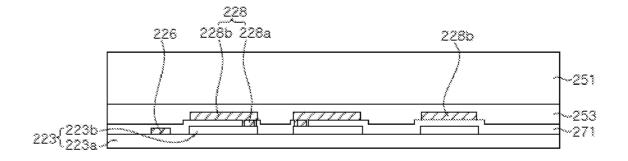

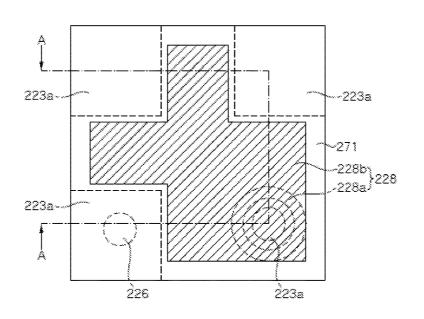

[0065] FIGS. 3A, 3B, 4A, 4B, 5A, 5B, 6A, 6B, 7A, 7B, 8A, 8B, 9A, 9B, 10A, 10B, 11A, 11B, 12A, 12B, 13A, 13B, 14A, 14B, 15A, 15B, 16A, and 16B are schematic plan views and schematic cross-sectional views illustrating a method of manufacturing a display apparatus according to an exemplary embodiment.

**[0066]** FIG. **17** is a schematic plan view of a display apparatus according to another exemplary embodiment.

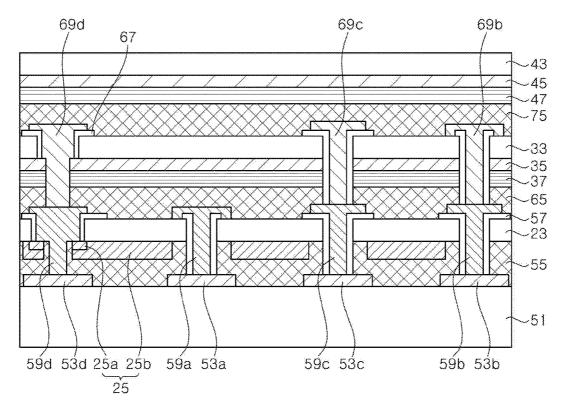

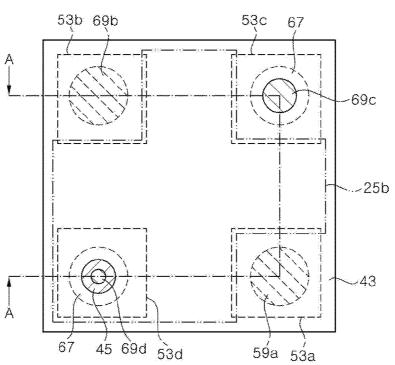

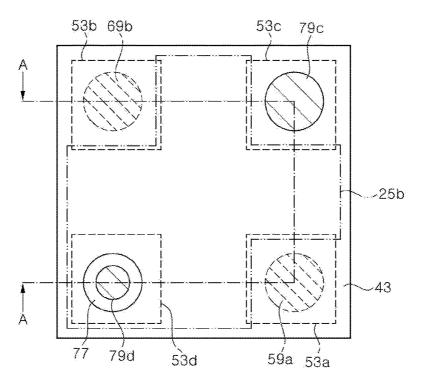

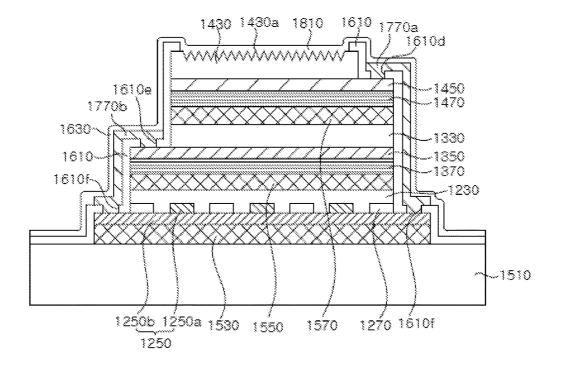

[0067] FIG. 18 is a schematic cross-sectional view taken along line B-B of FIG. 17.

**[0068]** FIG. **19** is a schematic circuit diagram of a display apparatus according to an exemplary embodiment.

**[0069]** FIG. **20** is a schematic plan view of a display apparatus according to an exemplary embodiment.

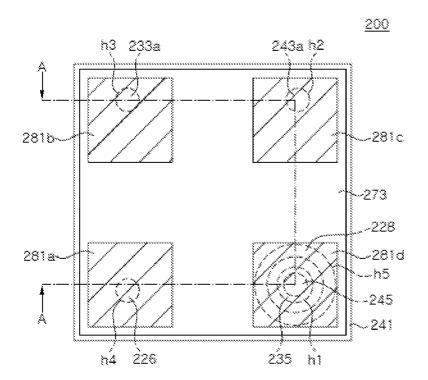

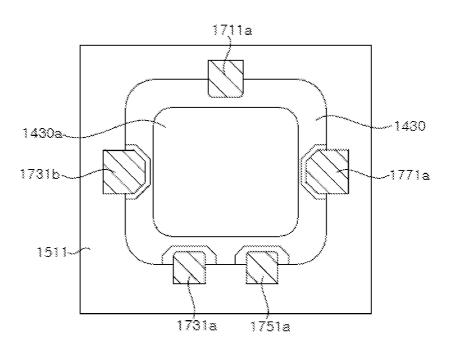

[0070] FIG. 21A is a schematic plan view of a light emitting device according to an exemplary embodiment.

**[0071]** FIG. **21**B is a schematic cross-sectional view taken along line A-A of FIG. **21**A.

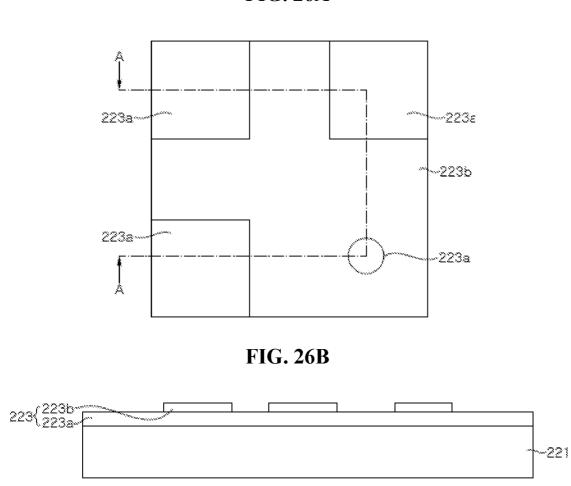

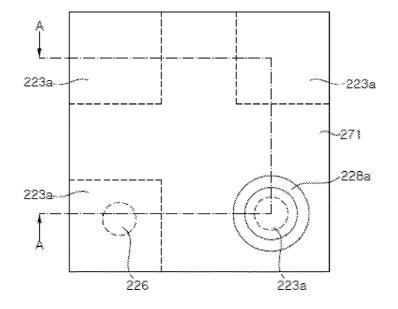

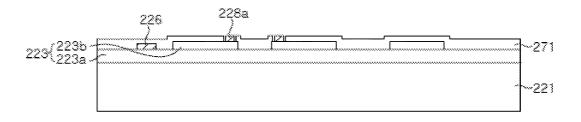

[0072] FIGS. 22, 23, 24, 25, 26A, 26B, 27A, 27B, 28A, 28B, 29, 30A, 30B, 31A, 31B, 32A, 32B, 33A, 33B, 34A, 34B, 35A, and 35B are schematic plan views and cross-sectional views illustrating a method of manufacturing a light emitting device according to an exemplary embodiment.

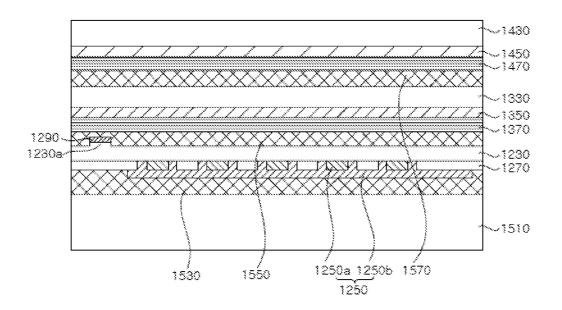

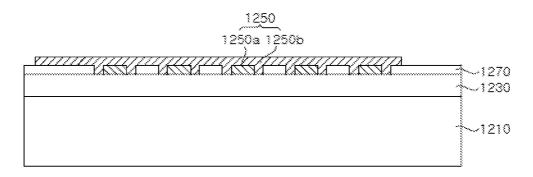

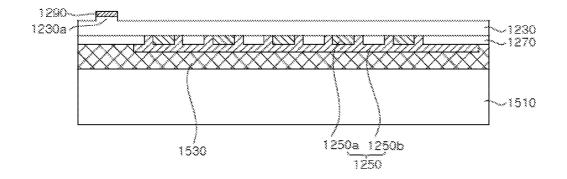

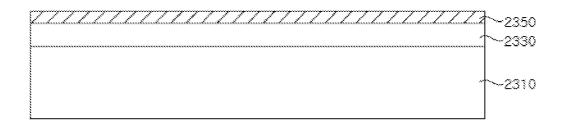

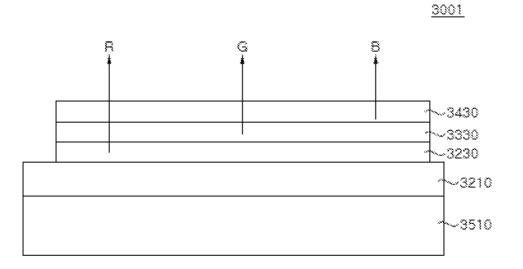

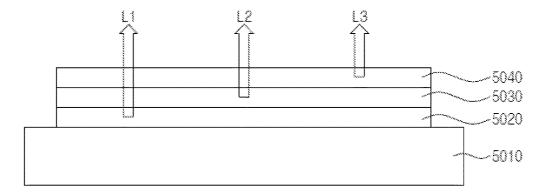

**[0073]** FIG. **36** is a schematic cross-sectional view of a light emitting diode stack for a display according to an exemplary embodiment.

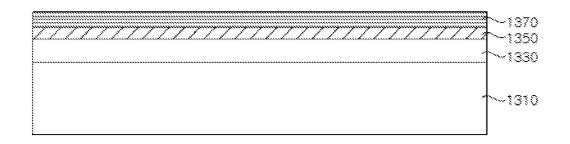

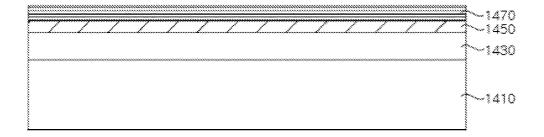

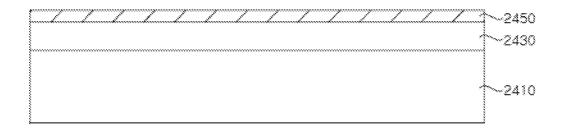

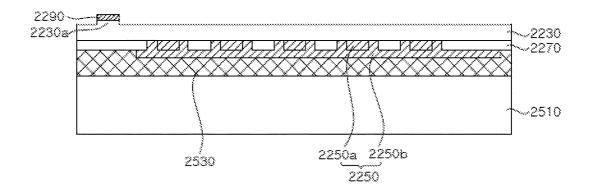

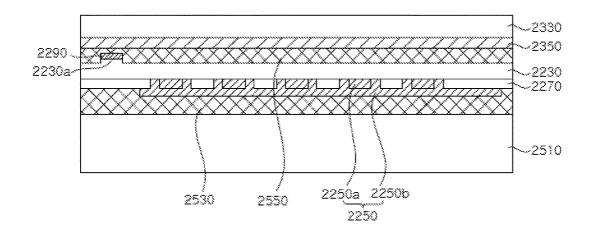

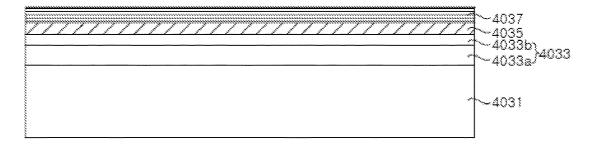

**[0074]** FIGS. **37**A, **37**B, **37**C, **37**D, and **37**E are schematic cross-sectional views illustrating a method of manufacturing a light emitting diode stack for a display according to an exemplary embodiment.

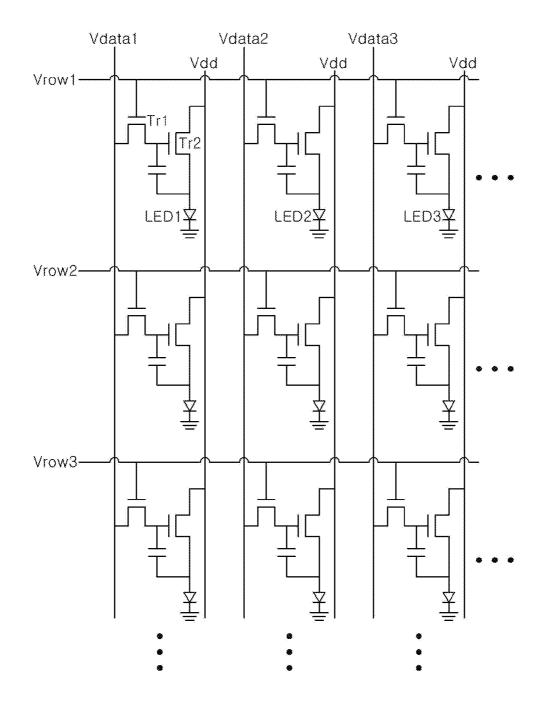

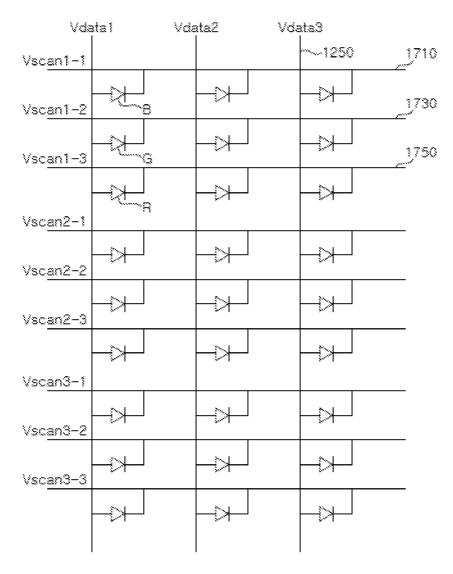

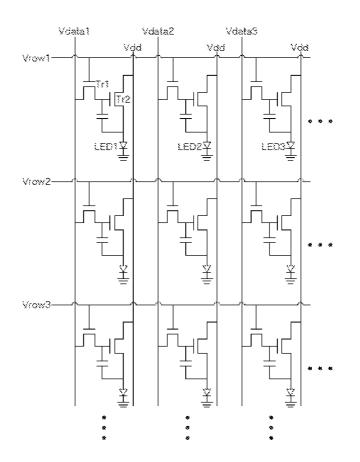

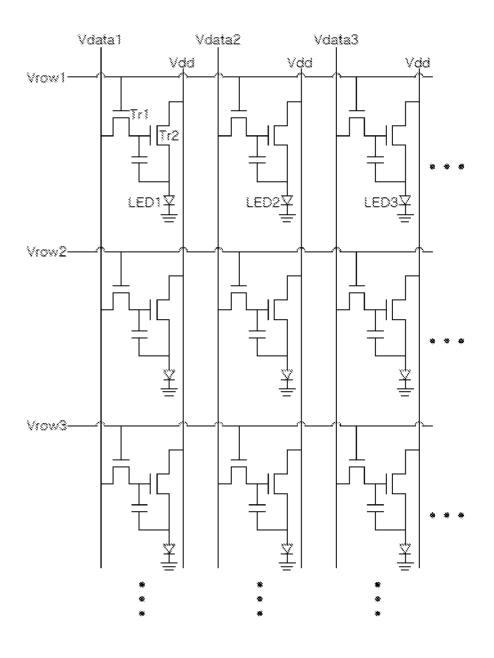

**[0075]** FIG. **38** is a schematic circuit diagram of a display apparatus according to an exemplary embodiment.

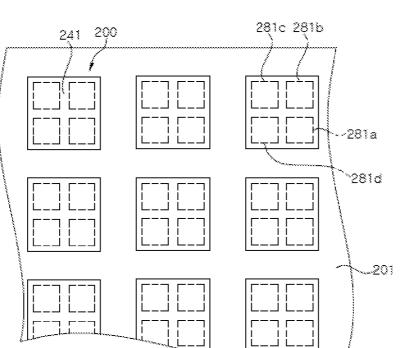

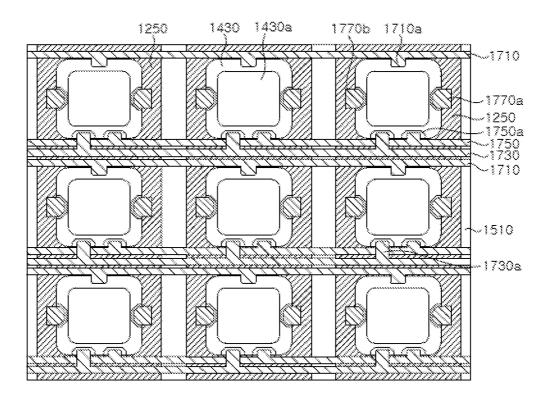

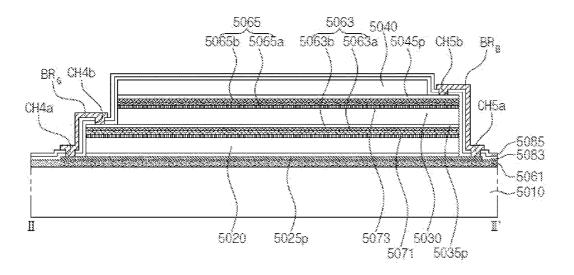

**[0076]** FIG. **39** is a schematic plan view of a display apparatus according to an exemplary embodiment.

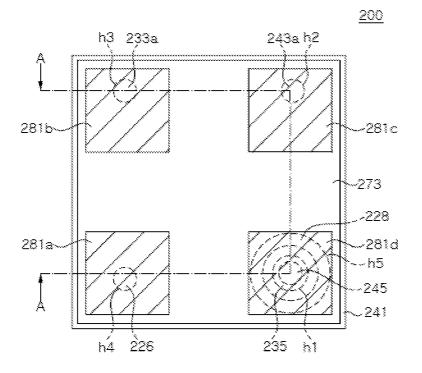

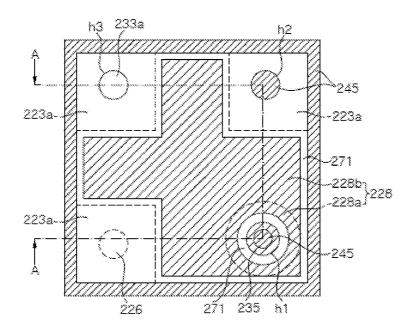

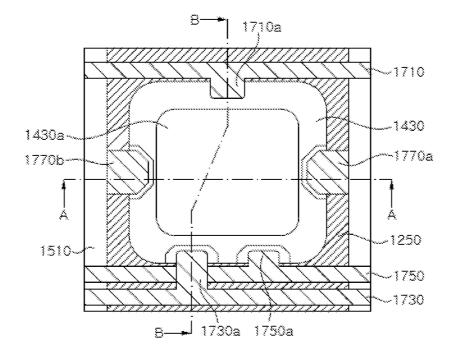

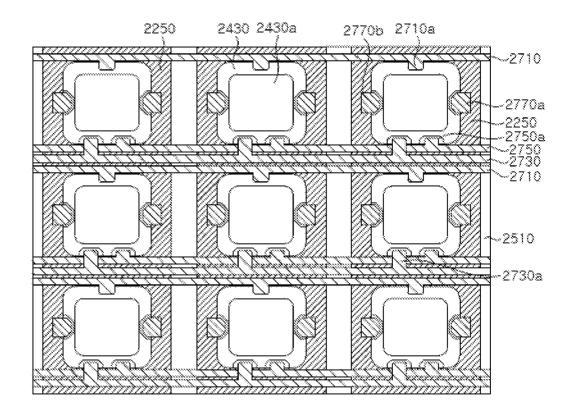

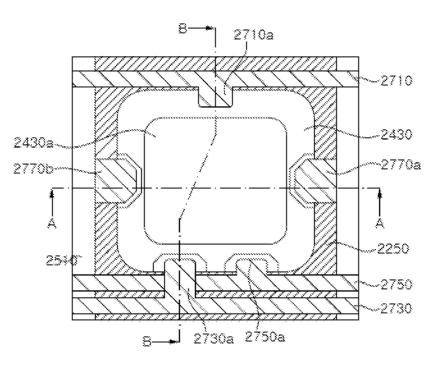

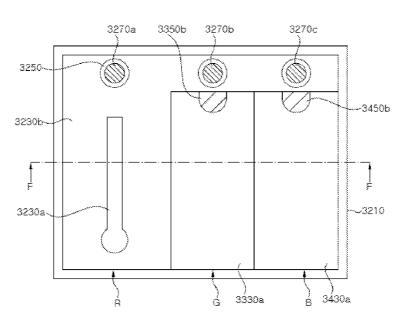

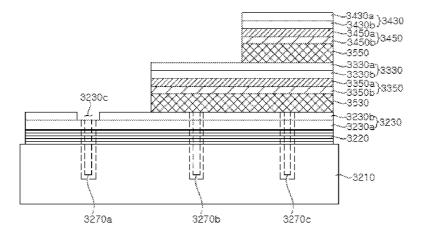

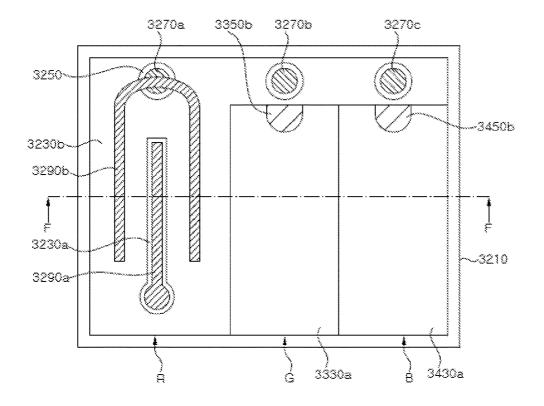

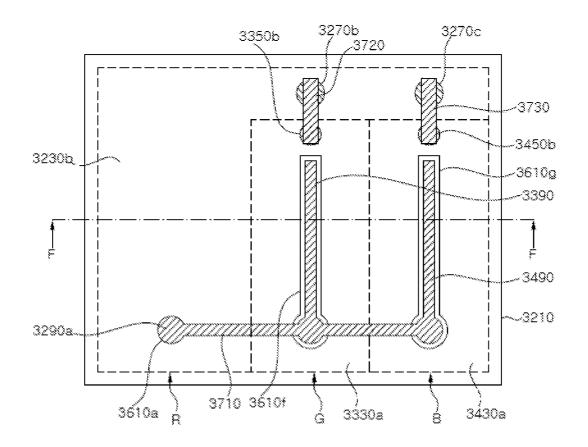

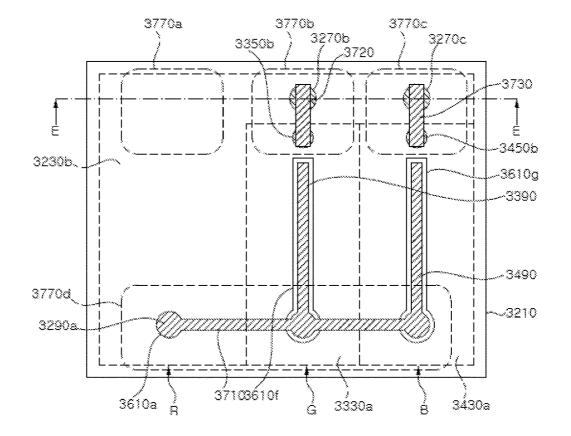

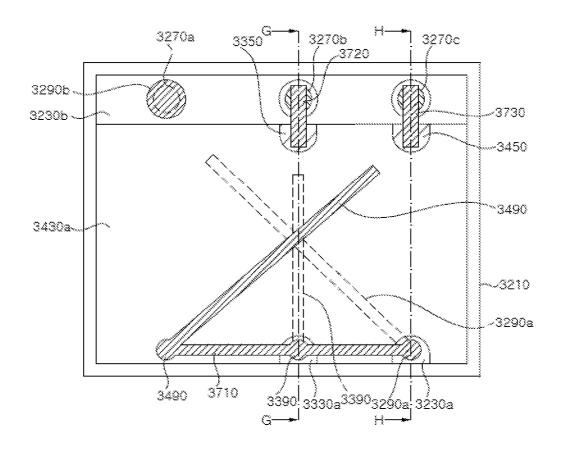

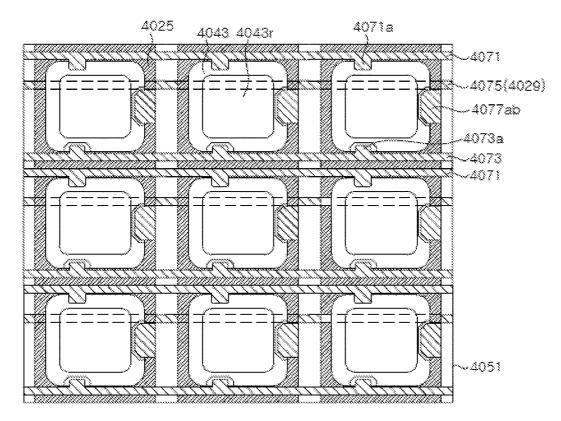

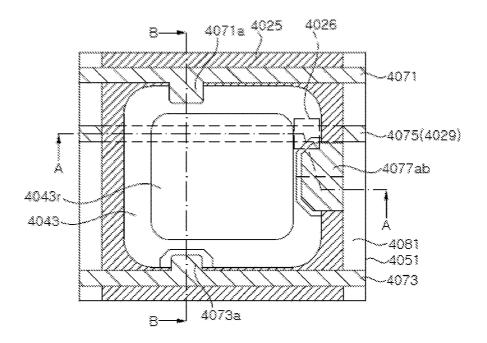

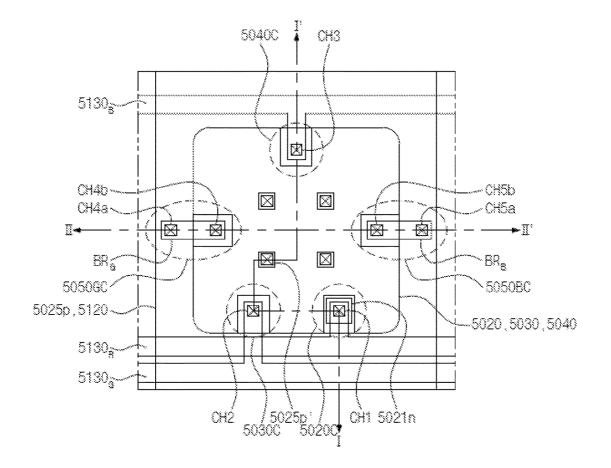

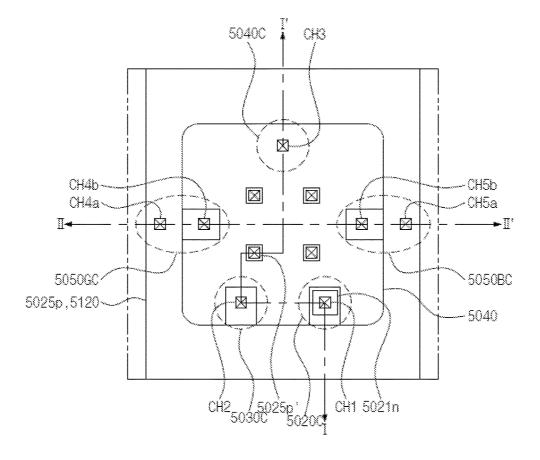

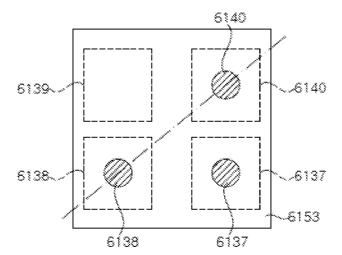

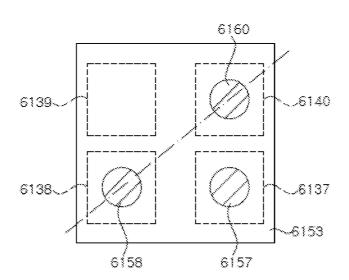

[0077] FIG. 40 is an enlarged plan view of one pixel of the display apparatus of FIG. 39.

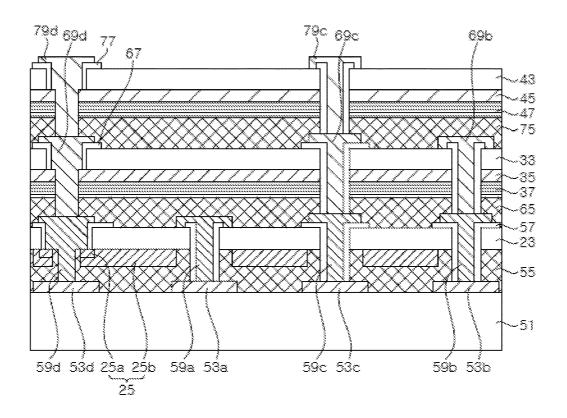

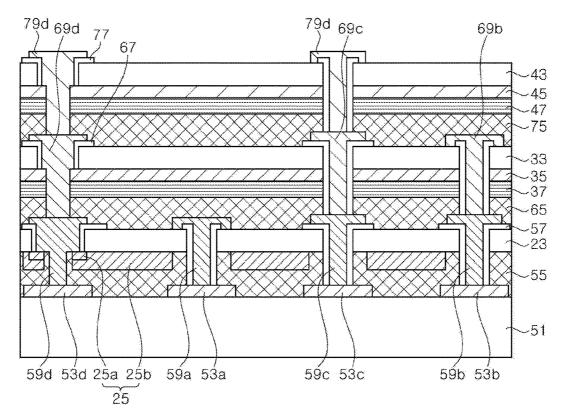

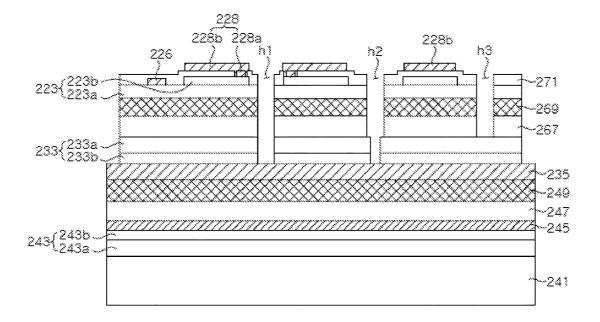

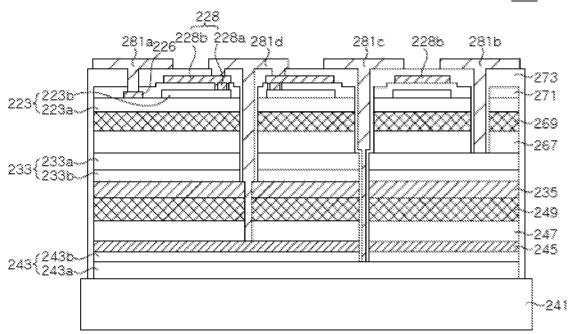

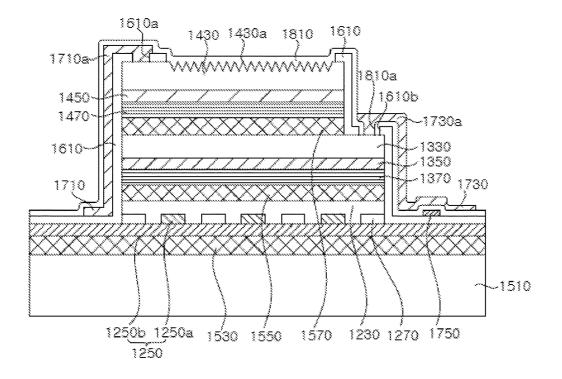

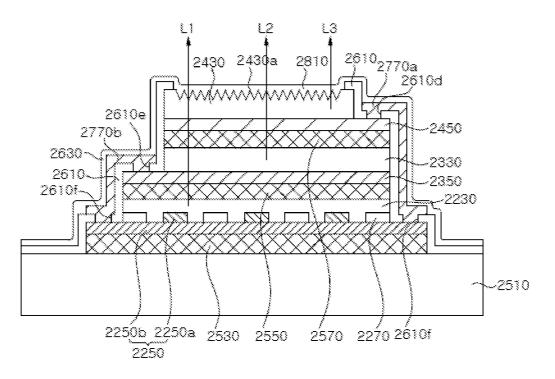

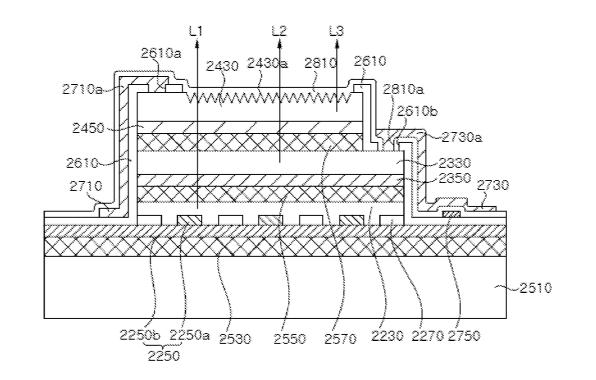

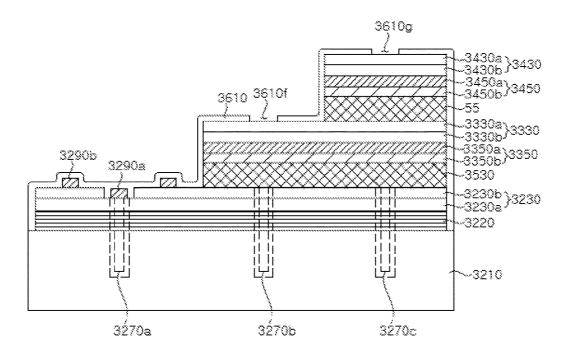

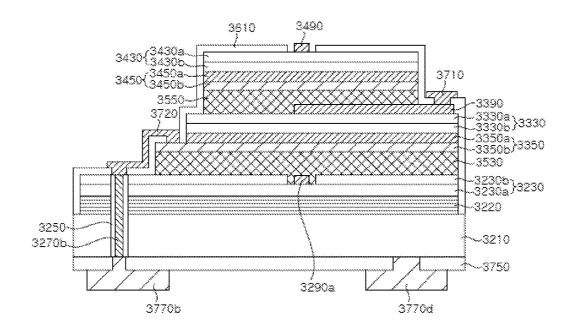

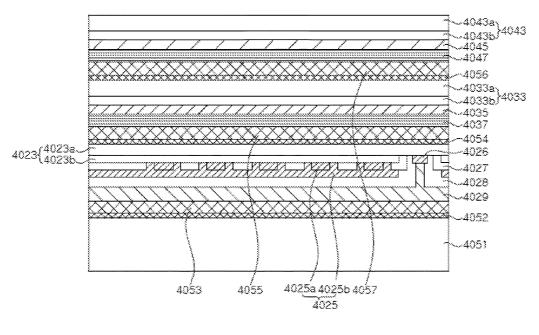

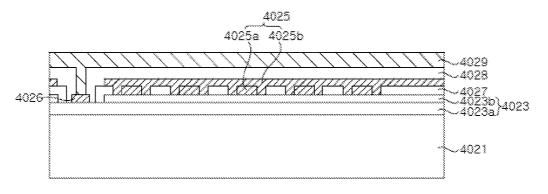

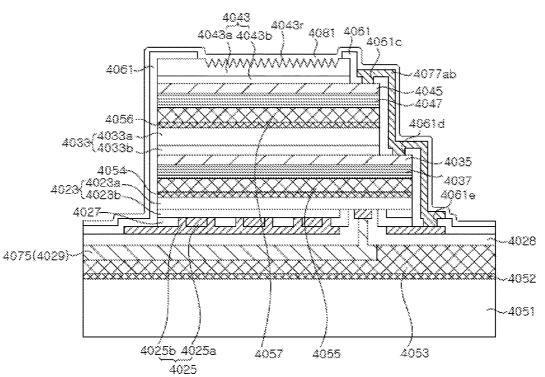

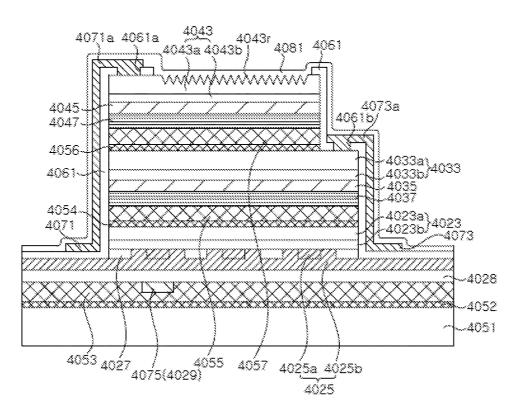

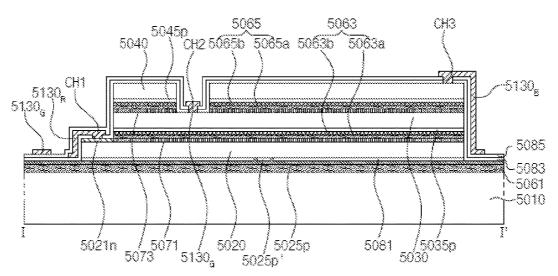

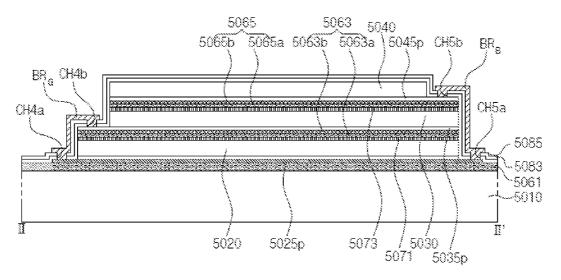

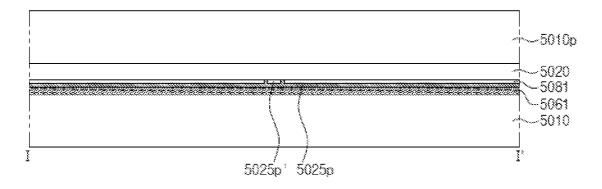

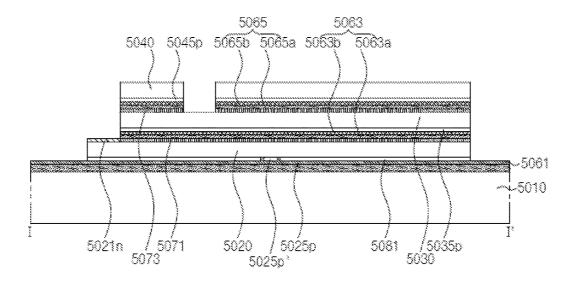

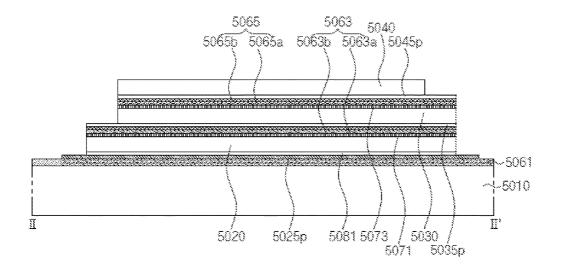

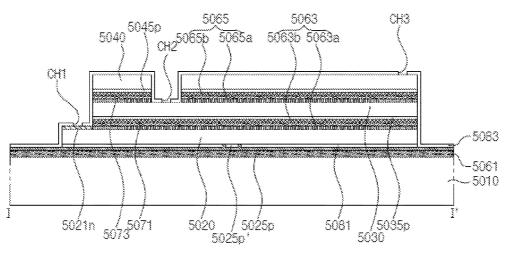

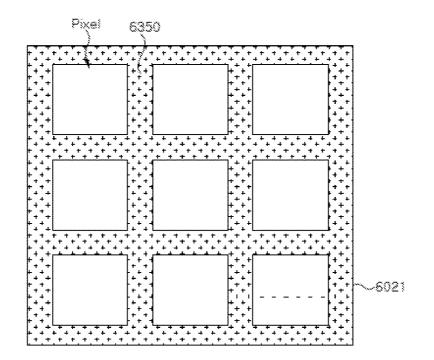

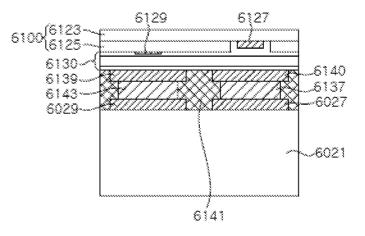

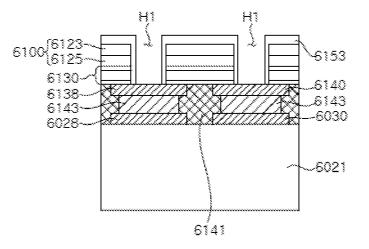

[0078] FIG. 41 is a schematic cross-sectional view taken along line A-A of FIG. 40.

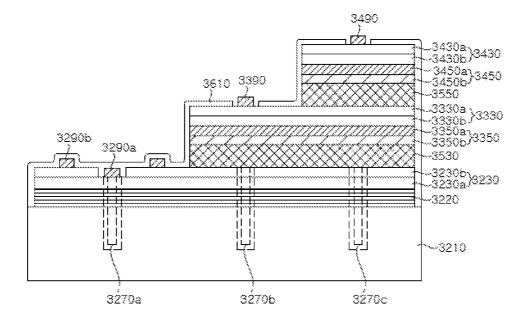

[0079] FIG. 42 is a schematic cross-sectional view taken along line B-B of FIG. 40.

**[0080]** FIGS. **43**A, **43**B, **43**C, **43**D, **43**E, **43**F, **43**G, **43**H, **43**I, **43**J, and **43**K are schematic cross-sectional views illustrating a method of manufacturing a display apparatus according to an exemplary embodiment.

**[0081]** FIG. **44** is a schematic circuit diagram of a display apparatus according to another exemplary embodiment.

**[0082]** FIG. **45** is a schematic plan view of a display apparatus according to another exemplary embodiment.

**[0083]** FIG. **46** is a schematic cross-sectional view of a light emitting diode stack for a display according to an exemplary embodiment.

**[0084]** FIGS. **47**A, **47**B, **47**C, **47**D, and **47**E are schematic cross-sectional views illustrating a method of manufacturing a light emitting diode stack for a display according to an exemplary embodiment.

**[0085]** FIG. **48** is a schematic circuit diagram of a display apparatus according to an exemplary embodiment.

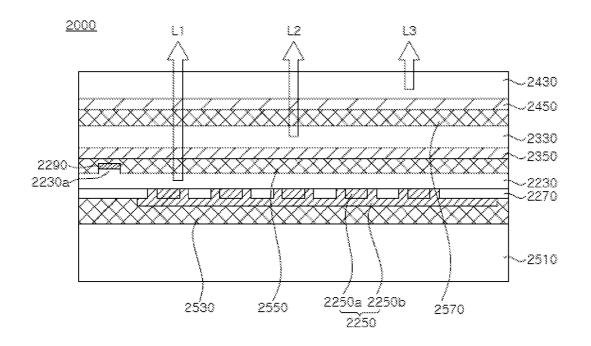

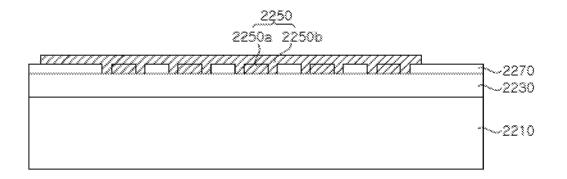

**[0086]** FIG. **49** is a schematic plan view of the display apparatus according to an exemplary embodiment.

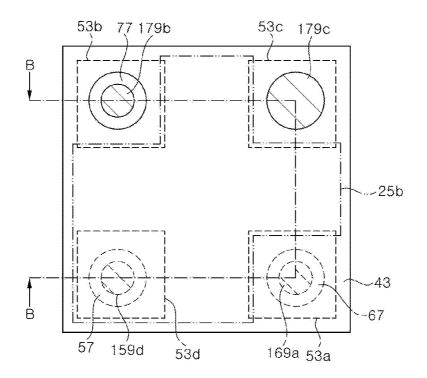

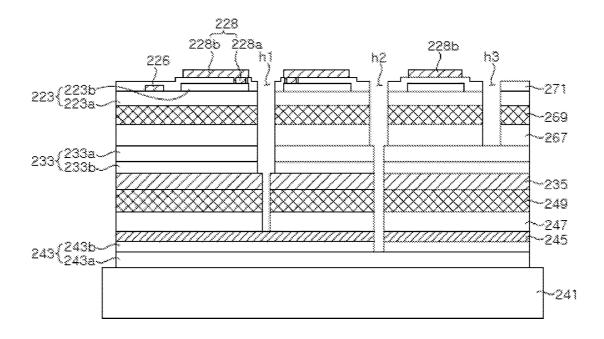

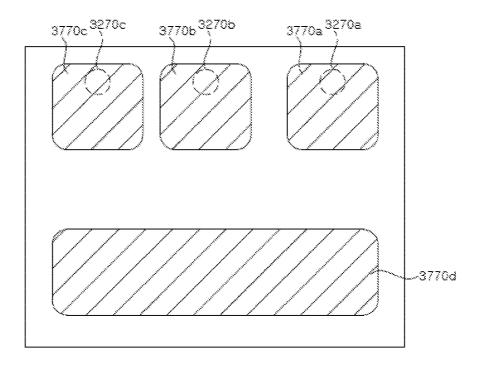

[0087] FIG. 50 is an enlarged plan view of one pixel of the display apparatus of FIG. 49.

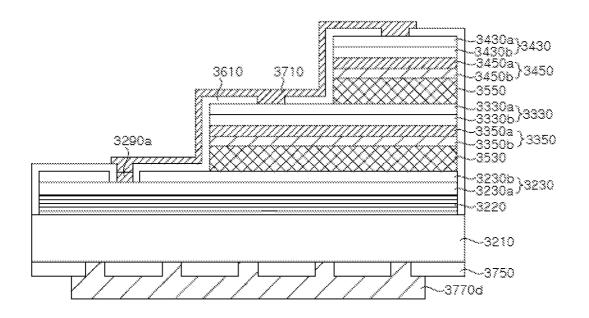

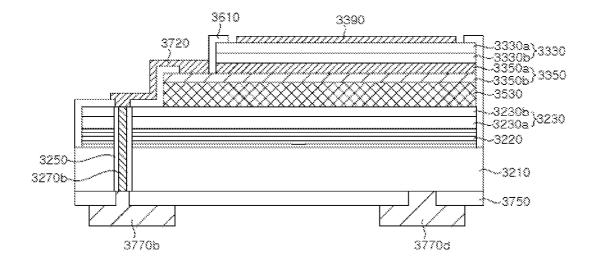

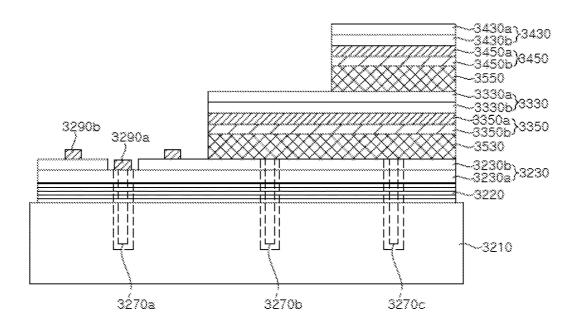

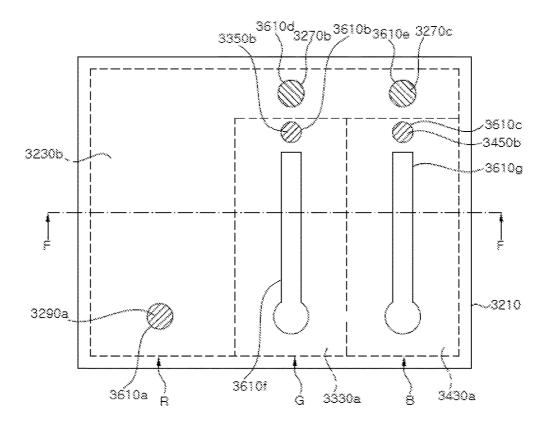

[0088] FIG. 51 is a schematic cross-sectional view taken along line A-A of FIG. 50.

**[0089]** FIG. **52** is a schematic cross-sectional view taken along line B-B of FIG. **50**.

**[0090]** FIGS. **53**A, **53**B, **53**C, **53**D, **53**E, **53**F, **53**G, **53**H, **53**I, **53**J, and **53**K are schematic cross-sectional views illustrating a method of manufacturing a display apparatus according to an exemplary embodiment.

**[0091]** FIG. **54** is a schematic circuit diagram of a display apparatus according to another exemplary embodiment.

**[0092]** FIG. **55** is a schematic plan view of a display apparatus according to another exemplary embodiment.

**[0093]** FIG. **56** is a schematic plan view of a display apparatus according to an exemplary embodiment.

**[0094]** FIG. **57** is a schematic cross-sectional view of a light emitting diode pixel for a display according to an exemplary embodiment.

**[0095]** FIG. **58** is a schematic circuit diagram of a display apparatus according to an exemplary embodiment.

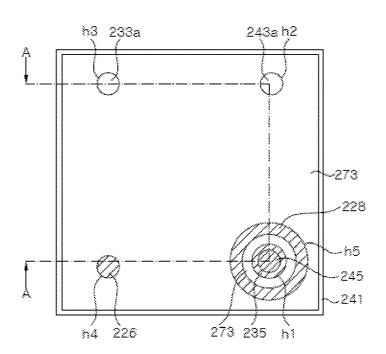

**[0096]** FIG. **59**A and FIG. **59**B are a top view and a bottom view of one pixel of a display apparatus according to an exemplary embodiment.

[0097] FIG. 60A is a schematic cross-sectional view taken along line A-A of FIG. 59A.

[0098] FIG. 60B is a schematic cross-sectional view taken along line B-B of FIG. 59A.

[0099] FIG. 60C is a schematic cross-sectional view taken along line C-C of FIG. 59A.

**[0100]** FIG. **60**D is a schematic cross-sectional view taken along line D-D of FIG. **59**A.

**[0101]** FIGS. **61**A, **61**B, **62**A, **62**B, **63**A, **63**B, **64**A, **64**B, **65**A, **65**B, **66**A, **66**B, **67**A, **67**B, **68**A, and **68**B are schematic plan views and schematic cross-sectional view illustrating a method of manufacturing a display apparatus according to an exemplary embodiment.

**[0102]** FIG. **69** is a schematic cross-sectional view of a light emitting diode pixel for a display according to another exemplary embodiment.

[0103] FIG. 70 is an enlarged top view of one pixel of a display apparatus according to an exemplary embodiment. [0104] FIG. 71A and FIG. 71B are cross-sectional views taken along lines G-G and H-H in FIG. 70, respectively.

**[0105]** FIG. **72** is a schematic cross-sectional view of a light emitting diode (LED) stack for a display according to an exemplary embodiment.

**[0106]** FIGS. **73**A, **73**B, **73**C, **73**D, **73**E, and **73**F are schematic cross-sectional views illustrating a method for manufacturing a light emitting diode stack for a display according to an exemplary embodiment.

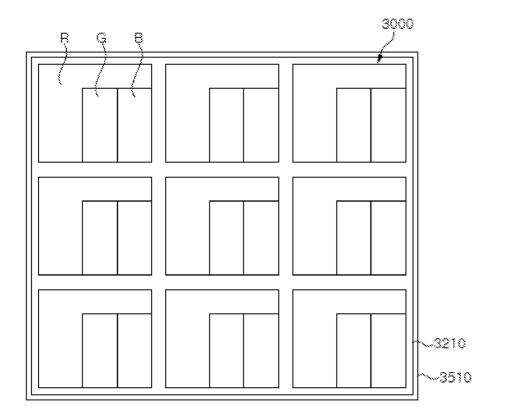

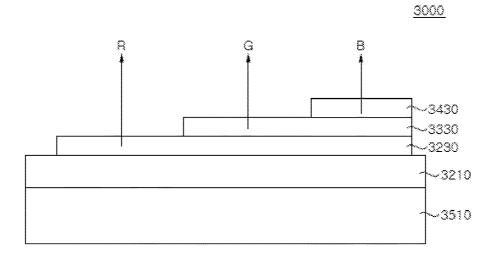

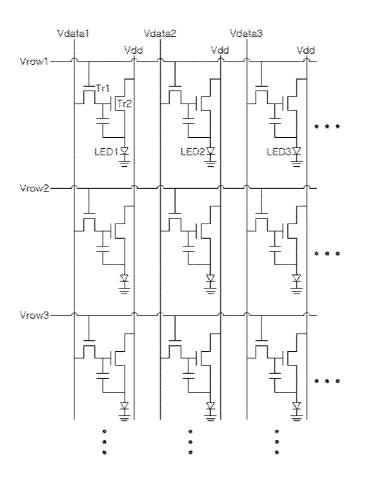

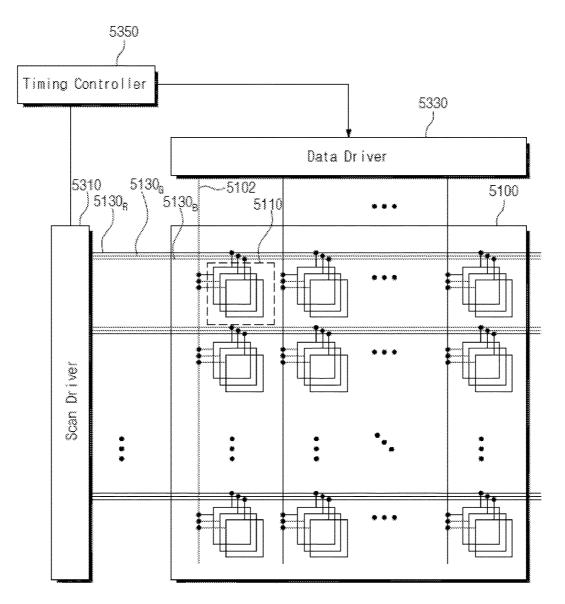

**[0107]** FIG. **74** is a schematic circuit diagram of a display apparatus according to an exemplary embodiment.

**[0108]** FIG. **75** is a schematic plan view of a display apparatus according to an exemplary embodiment.

**[0109]** FIG. **76** is an enlarged plan view of one pixel of the display apparatus of FIG. **75**.

[0110] FIG. 77 is a schematic cross-sectional view taken along line A-A of FIG. 76.

**[0111]** FIG. **78** is a schematic cross-sectional view taken along line B-B of FIG. **76**.

**[0112]** FIGS. **79A**, **79B**, **79C**, **79D**, **79E**, **79F**, **79G**, and **79H** are schematic plan views illustrating a method for manufacturing a display apparatus according to an exemplary embodiment.

**[0113]** FIG. **80** is a schematic cross-sectional view of a light emitting stacked structure according to an exemplary embodiment.

**[0114]** FIGS. **81**A and **81**B are cross-sectional views of a light emitting stacked structure according to exemplary embodiments.

**[0115]** FIG. **82** is a cross-sectional view of a light emitting stacked structure including a wiring part according to an exemplary embodiment.

**[0116]** FIG. **83** is a cross-section view of a light emitting stacked structure according to an exemplary embodiment.

**[0117]** FIG. **84** is a plan view of a display device according to an exemplary embodiment.

**[0118]** FIG. **85** is an enlarged plan view of portion P1 of FIG. **84**.

**[0119]** FIG. **86** is a structural diagram of a display device according to an exemplary embodiment.

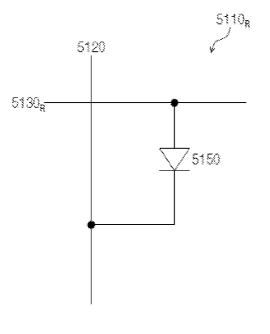

**[0120]** FIG. **87** is a circuit diagram of one pixel of a passive type display device.

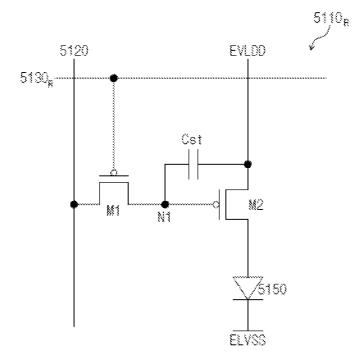

**[0121]** FIG. **88** is a circuit diagram of one pixel of an active type display device.

**[0122]** FIG. **89** is a plan view of a pixel according to an exemplary embodiment.

**[0123]** FIGS. **90**A and **90**B are cross-sectional views taken along lines I-I' and II-II' of FIG. **89**, respectively.

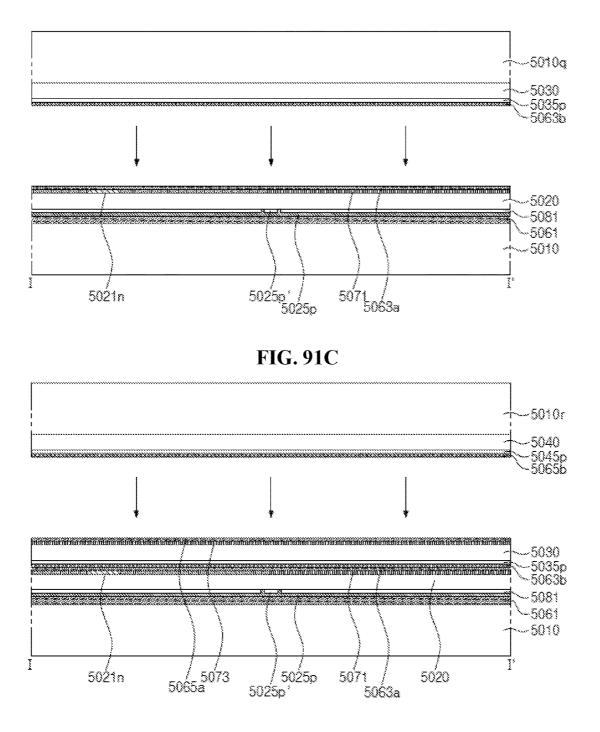

**[0124]** FIGS. **91**A, **91**B, and **91**C are cross-sectional views taken along line I-I' in FIG. **89**, illustrating a process of stacking first to third epitaxial stacks on a substrate according to an exemplary embodiment.

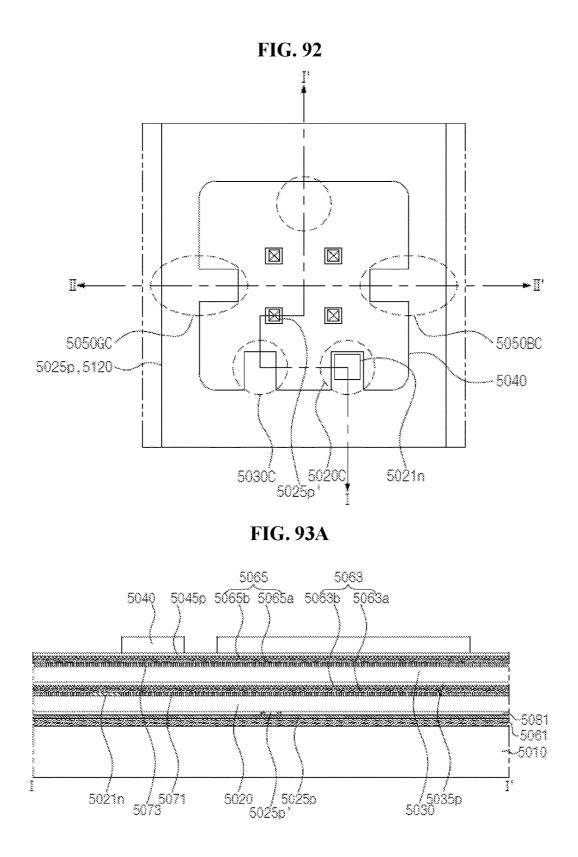

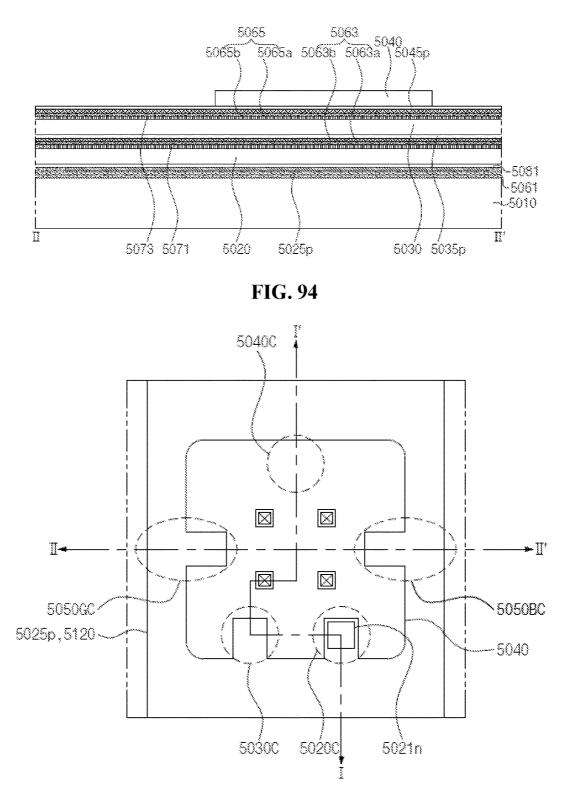

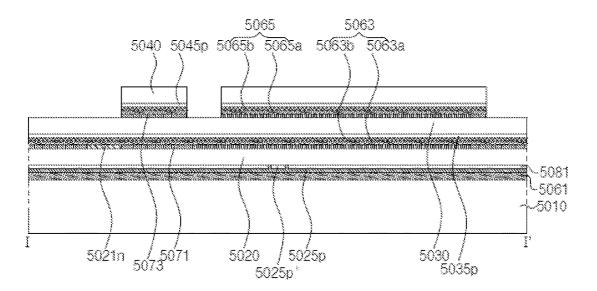

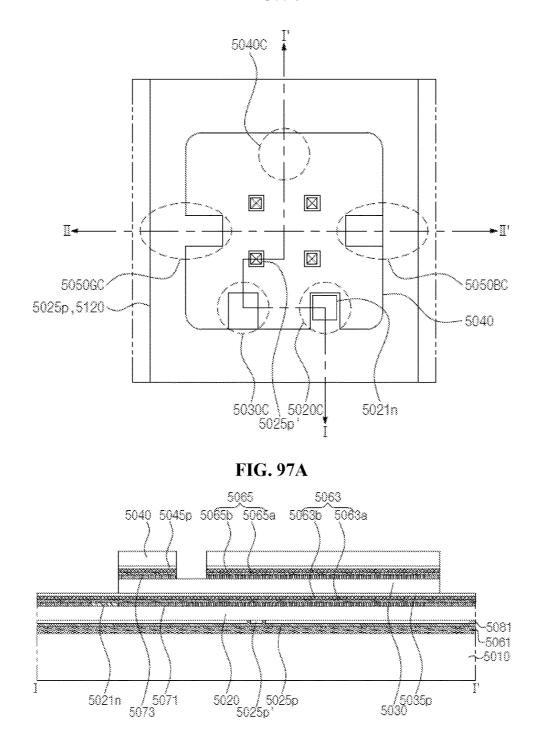

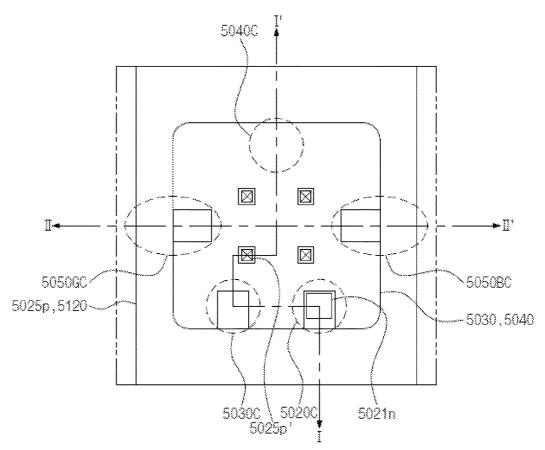

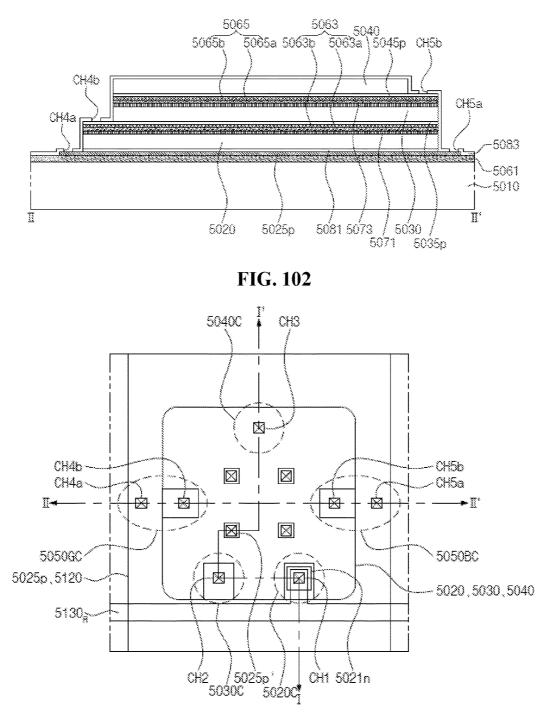

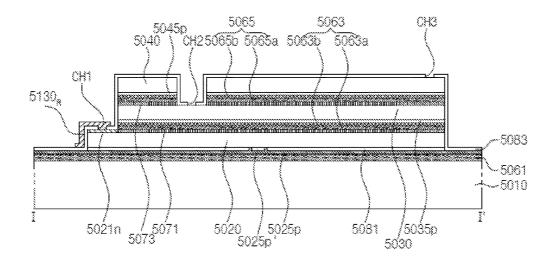

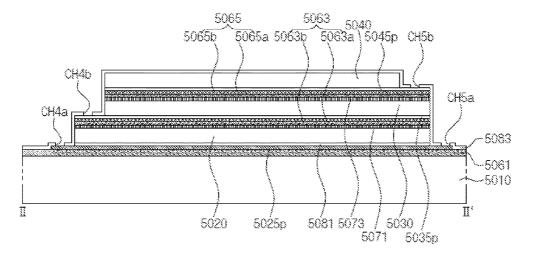

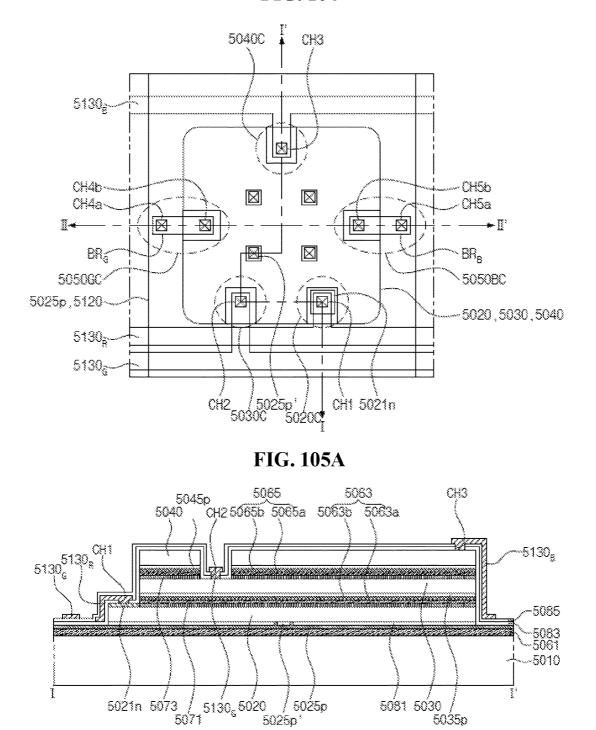

**[0125]** FIGS. **92**, **94**, **96**, **98**, **100**, **102**, **104** are plan views sequentially illustrating a method of manufacturing a pixel on a substrate.

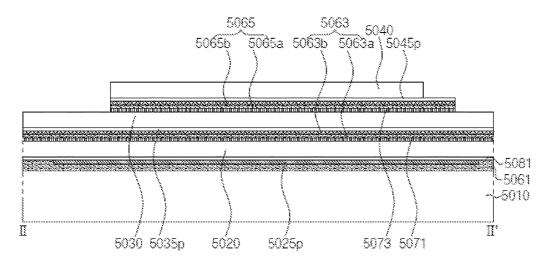

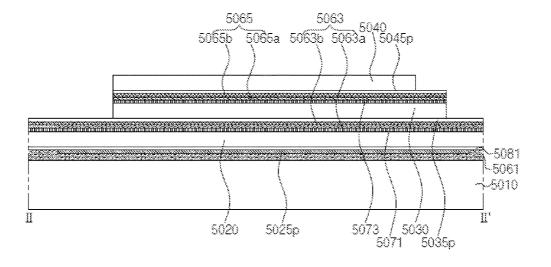

[0126] FIGS. 93A, 95A, 97A, 99A, 101A, 103A, and 105A are cross-sectional views taken along line I-I' of FIGS. 92, 94, 96, 98, 100, 102, 104, respectively.

[0127] FIGS. 93B, 95B, 97B, 99B, 101B, 103B, and 105B are cross-sectional views taken along line II-II' of FIGS. 92, 94, 96, 98, 100, 102, 104, respectively.

**[0128]** FIG. **106** is a schematic plan view of a display apparatus according to an exemplary embodiment.

**[0129]** FIG. **107**A is a cross-sectional view of the display apparatus of FIG. **106**.

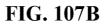

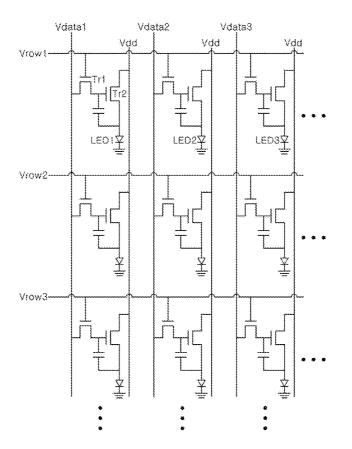

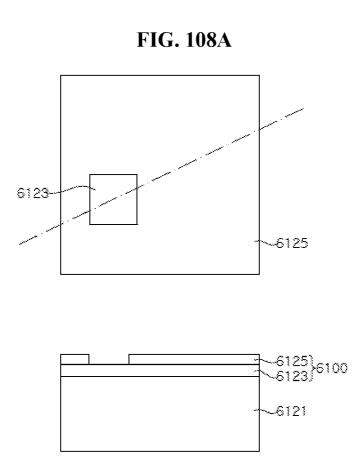

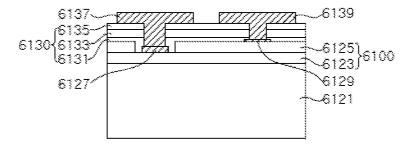

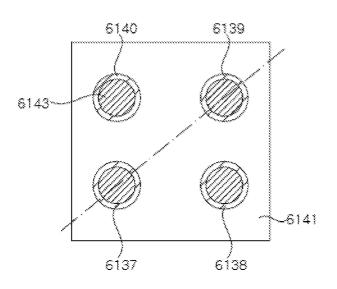

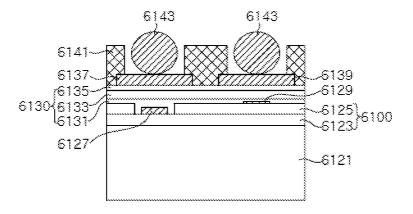

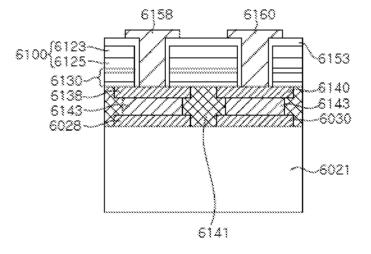

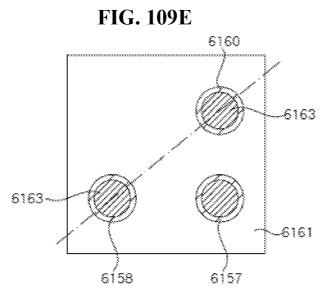

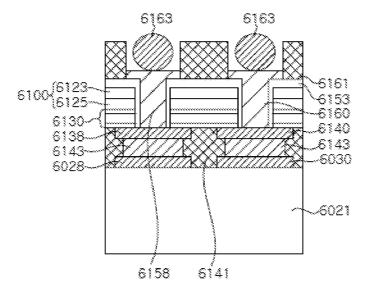

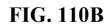

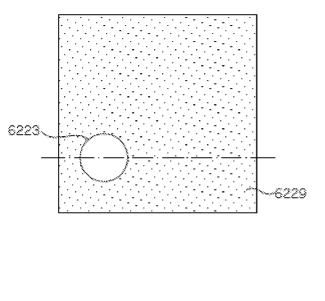

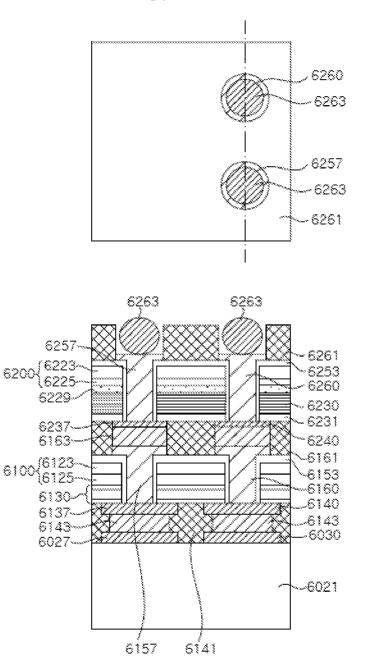

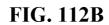

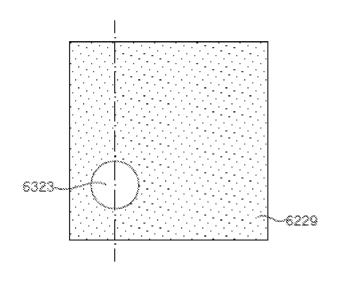

[0130] FIG. 107B is a schematic circuit diagram of a display apparatus according to an exemplary embodiment. [0131] FIGS. 108A, 108B, 108C, 108D, 108E, 109A, 109B, 109C, 109D, 109E, 110A, 110B, 110C, 110D, 111A, 111B, 111C, 111D, 112A, 112B, 112C, 112D, 113A, 113B, and 114 are schematic plan views and cross-sectional views illustrating a manufacturing method of a display apparatus according to an exemplary embodiment.

**[0132]** FIGS. **115**A, **115**B, and **115**C are schematic crosssectional views of a metal bonding material according to exemplary embodiments.

#### DETAILED DESCRIPTION

[0133] In the following description, for the purposes of explanation, numerous specific details are set forth in order to provide a thorough understanding of various exemplary embodiments or implementations of the invention. As used herein "embodiments" and "implementations" are interchangeable words that are non-limiting examples of devices or methods employing one or more of the inventive concepts disclosed herein. It is apparent, however, that various exemplary embodiments may be practiced without these specific details or with one or more equivalent arrangements. In other instances, well-known structures and devices are shown in block diagram form in order to avoid unnecessarily obscuring various exemplary embodiments. Further, various exemplary embodiments may be different, but do not have to be exclusive. For example, specific shapes, configurations, and characteristics of an exemplary embodiment may be used or implemented in another exemplary embodiment without departing from the inventive concepts.

**[0134]** Unless otherwise specified, the illustrated exemplary embodiments are to be understood as providing exemplary features of varying detail of some ways in which the inventive concepts may be implemented in practice. Therefore, unless otherwise specified, the features, components, modules, layers, films, panels, regions, and/or aspects, etc. (hereinafter individually or collectively referred to as "elements"), of the various embodiments may be otherwise combined, separated, interchanged, and/or rearranged without departing from the inventive concepts.

**[0135]** The use of cross-hatching and/or shading in the accompanying drawings is generally provided to clarify boundaries between adjacent elements. As such, neither the presence nor the absence of cross-hatching or shading conveys or indicates any preference or requirement for particular materials, material properties, dimensions, proportions, commonalities between illustrated elements, and/ or any other characteristic, attribute, property, etc., of the elements, unless specified. Further, in the accompanying drawings, the size and relative sizes of elements may be exaggerated for clarity and/or descriptive purposes. When an exemplary embodiment may be implemented differently, a specific process order may be performed differently from the described order. For example, two consecutively described processes may be performed substantially at the

same time or performed in an order opposite to the described order. Also, like reference numerals denote like elements.

[0136] When an element, such as a layer, is referred to as being "on," "connected to," or "coupled to" another element or layer, it may be directly on, connected to, or coupled to the other element or layer or intervening elements or layers may be present. When, however, an element or layer is referred to as being "directly on," "directly connected to," or "directly coupled to" another element or layer, there are no intervening elements or layers present. To this end, the term "connected" may refer to physical, electrical, and/or fluid connection, with or without intervening elements. Further, the D1-axis, the D2-axis, and the D3-axis are not limited to three axes of a rectangular coordinate system, such as the x, y, and z-axes, and may be interpreted in a broader sense. For example, the D1-axis, the D2-axis, and the D3-axis may be perpendicular to one another, or may represent different directions that are not perpendicular to one another. For the purposes of this disclosure, "at least one of X, Y, and Z" and "at least one selected from the group consisting of X, Y, and Z" may be construed as X only, Y only, Z only, or any combination of two or more of X, Y, and Z, such as, for instance, XYZ, XYY, YZ, and ZZ. As used herein, the term "and/or" includes any and all combinations of one or more of the associated listed items.

**[0137]** Although the terms "first," "second," etc. may be used herein to describe various types of elements, these elements should not be limited by these terms. These terms are used to distinguish one element from another element. Thus, a first element discussed below could be termed a second element without departing from the teachings of the disclosure.

[0138] Spatially relative terms, such as "beneath," "below," "under," "lower," "above," "upper," "over," "higher," "side" (e.g., as in "sidewall"), and the like, may be used herein for descriptive purposes, and, thereby, to describe one elements relationship to another element(s) as illustrated in the drawings. Spatially relative terms are intended to encompass different orientations of an apparatus in use, operation, and/or manufacture in addition to the orientation depicted in the drawings. For example, if the apparatus in the drawings is turned over, elements described as "below" or "beneath" other elements or features would then be oriented "above" the other elements or features. Thus, the exemplary term "below" can encompass both an orientation of above and below. Furthermore, the apparatus may be otherwise oriented (e.g., rotated 90 degrees or at other orientations), and, as such, the spatially relative descriptors used herein interpreted accordingly.

**[0139]** The terminology used herein is for the purpose of describing particular embodiments and is not intended to be limiting. As used herein, the singular forms, "a," "an," and "the" are intended to include the plural forms as well, unless the context clearly indicates otherwise. Moreover, the terms "comprises," "comprising," "includes," and/or "including," when used in this specification, specify the presence of stated features, integers, steps, operations, elements, components, and/or groups thereof, but do not preclude the presence or addition of one or more other features, integers, steps, operations, elements, components, and/or groups thereof. It is also noted that, as used herein, the terms "substantially," "about," and other similar terms, are used as terms of approximation and not as terms of degree, and, as such, are utilized to account for inherent deviations in

measured, calculated, and/or provided values that would be recognized by one of ordinary skill in the art.

**[0140]** Various exemplary embodiments are described herein with reference to sectional and/or exploded illustrations that are schematic illustrations of idealized exemplary embodiments and/or intermediate structures. As such, variations from the shapes of the illustrations as a result, for example, of manufacturing techniques and/or tolerances, are to be expected. Thus, exemplary embodiments disclosed herein should not necessarily be construed as limited to the particular illustrated shapes of regions, but are to include deviations in shapes that result from, for instance, manufacturing. In this manner, regions illustrated in the drawings may be schematic in nature and the shapes of these regions may not reflect actual shapes of regions of a device and, as such, are not necessarily intended to be limiting.

**[0141]** Unless otherwise defined, all terms (including technical and scientific terms) used herein have the same meaning as commonly understood by one of ordinary skill in the art to which this disclosure is a part. Terms, such as those defined in commonly used dictionaries, should be interpreted as having a meaning that is consistent with their meaning in the context of the relevant art and should not be interpreted in an idealized or overly formal sense, unless expressly so defined herein.

**[0142]** As used herein, a light emitting device or a light emitting diode according to exemplary embodiments may include a micro LED, which has a surface area less than about 10,000 square m as known in the art. In other exemplary embodiments, the micro LED's may have a surface area of less than about 4,000 square rim, or less than about 2,500 square rim, depending upon the particular application.

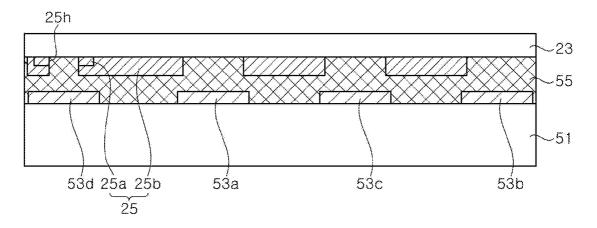

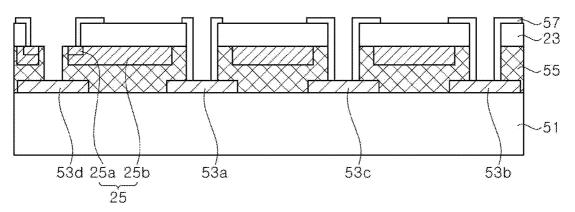

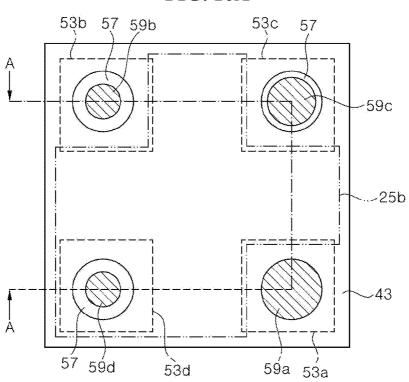

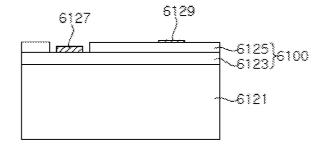

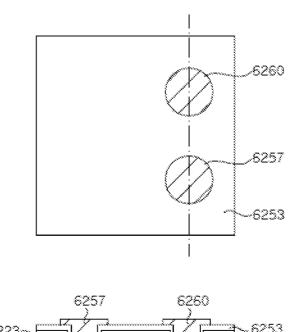

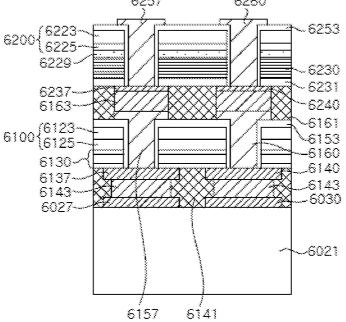

**[0143]** FIG. **1** is a schematic plan view of a display apparatus according to an exemplary embodiment. FIG. **2** is a schematic cross-sectional view taken along line A-A of FIG. **1**.

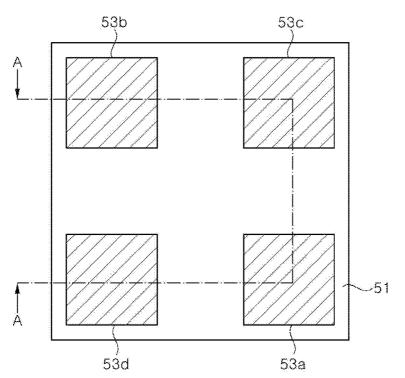

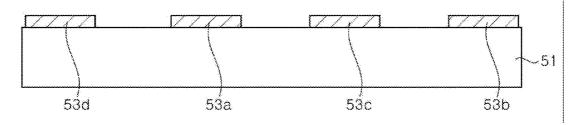

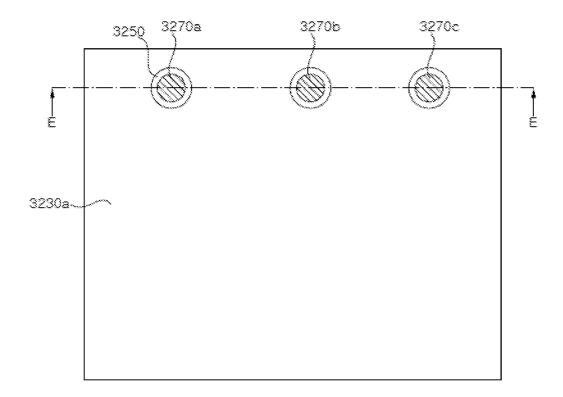

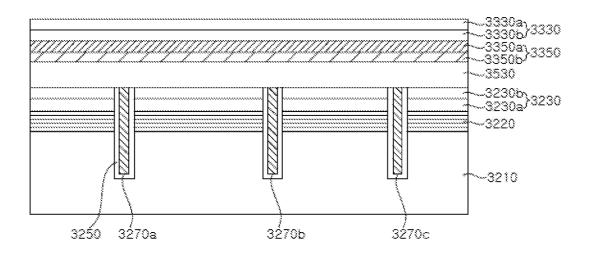

[0144] Referring to FIGS. 1 and 2, the display apparatus may include a substrate 51, electrode pads 53a, 53b, 53c, and 53d, a first LED stack 23, a second LED stack 33, a third LED stack 43, a first reflective electrode 25, a second transparent electrode 35, a third transparent electrode 45, a first color filter 37, a second color filter 47, a first bonding layer 55, a second bonding layer 65, and a third bonding layer 75. In addition, the display apparatus may include a plurality of connectors 59a, 59b, 59c, 59d, 69b, 69c, 69d, 79c, and 79d and insulating layers 57, 67, and 77. As used herein, a connector may be any type of structure, including through holes, vias, wires, lines, conductive material, and the like, that serves to electrically and/or mechanically connect two elements, such as layers.

**[0145]** The substrate **51** supports the LED stacks **23**, **33**, and **43**. In addition, the substrate **51** may have an internal circuit. For example, the substrate **51** may be a silicon substrate in which thin film transistors are formed. TFT substrates have been widely used in display fields, such as LCD display fields, for driving a display apparatus in an active matrix manner. Since TFT substrates are well known in the art, detailed descriptions of a structure of a TFT substrate will be omitted.

**[0146]** Although FIGS. **1** and **2** show one unit pixel disposed on the substrate **51**, a plurality of the unit pixels may be arranged on the substrate **51**, and the plurality of the unit pixels may be driven in an active matrix manner.

[0147] The electrode pads 53a, 53b, 53c, and 53d are exposed on the substrate 51. Each of the electrode pads 53a, 53b, 53c, and 53d are connected to one of the subpixels of the unit pixel disposed on the substrate 51, but the electrode pad 53d is connected to each of the three subpixels. Each of the electrode pads 53a, 53b, 53c, and 53d may be connected to the internal circuit of the substrate 51.

**[0148]** The first LED stack **23**, the second LED stack **33**, and the third LED stack **43** each include an n-type semiconductor layer, a p-type semiconductor layer, and an active layer interposed therebetween. The active layer may have a multi-quantum well structure.

[0149] The closer to the substrate 51, the longer wavelength light may be emitted from the LED stacks. For example, the first LED stack 23 may be an inorganic light emitting diode configured to emit red light, the second LED stack 33 may be an inorganic light emitting diode configured to emit green light, and the third LED stack 43 may be an inorganic light emitting diode configured to emit blue light. The first LED stack 23 may include a GaInP-based well layer and the second LED stack 33 and the third LED stack 43 may include a GaInN-based well layer. However, the inventive concepts are not limited thereto, and when the pixel includes a micro LED, the first LED stack 23 may emit any one of red, green, and blue light, and the second and third LED stacks 33 and 43 may emit different one of red, green, and blue light, without adversely affection operation due to small form factor of a micro LED.

**[0150]** The surfaces of each of the LED stacks **23**, **33**, and **43** may be an n-type semiconductor layer and a p-type semiconductor layer, respectively. Hereinafter, an upper surface and a lower surface of each of the first to third LED stacks **23**, **33**, and **43** will be described as an n-type and a p-type, respectively. However, the inventive concepts are not limited thereto, and the type of the upper surface and the lower surface of each of the LED stacks may be reversed or variously modified.

[0151] When the upper surface of the third LED stack 43 is an n-type, the upper surface of the third LED stack 43 may be surface textured by chemical etching or the like to form a roughened surface. The upper surfaces of the first LED stack 23 and the second LED stack 33 may also be subjected to surface texturing. However, when the second LED stack 33 emits green light, since green light has higher visibility than red light and blue light, it may be preferable to increase light emitting efficiency of the first LED stack 23 and the third LED stack 43 to the greater extent than that of the second LED stack 33. As such, the first LED stack 23 and the third LED stack 43 may be surface textured to improve light extraction efficiency without surface texturing the second LED stack 33. In this manner, light intensities of red light, green light, and the blue light may be balanced and adjusted to have substantially similar levels.

[0152] The first LED stack 23 is disposed close to the support substrate 51, the second LED stack 33 is disposed on the first LED stack 23, and the third LED stack 43 is disposed on the second LED stack 33. Since the first LED stack 23 may emit light having a longer wavelength than the second and third LED stacks 33 and 43, the light generated from the first LED stack 23 may be transmitted through the second and third LED stacks 33 and 43 and be emitted to the outside. In addition, since the second LED stack 33 may emit light having a longer wavelength than the third LED stack 34 may be transmitted to the outside. In addition, since the second LED stack 33 may emit light having a longer wavelength than the third LED stack 34 may emit light having a longer wavelength than the third LED stack 35 may emit light having a longer wavelength than the third LED stack 35 may emit light having a longer wavelength than the third LED stack 35 may emit light having a longer wavelength than the third LED stack 35 may emit light having a longer wavelength than the third LED stack 35 may emit light having a longer wavelength than the third LED stack 35 may emit light having a longer wavelength than the third LED stack 35 may emit light having a longer wavelength than the third LED stack 35 may emit light having a longer wavelength than the third LED stack 35 may emit light having a longer wavelength than the third LED stack 35 may emit light having a longer wavelength than the third LED stack 35 may emit light having a longer wavelength than the third LED stack 35 may emit light having a longer wavelength than the third LED stack 35 may emit light having a longer wavelength than the third LED stack 35 may emit light having a longer wavelength than the third LED stack 35 may emit light having a longer wavelength than the third LED stack 35 may emit light having a longer wavelength than the third LED stack 35 may emit light having a longer wavelength than the third LED stack 35 may emit light having a longer wavelength than the

stack **43**, the light generated from the second LED stack **33** may be transmitted through the third LED stack **43** and be emitted to the outside.

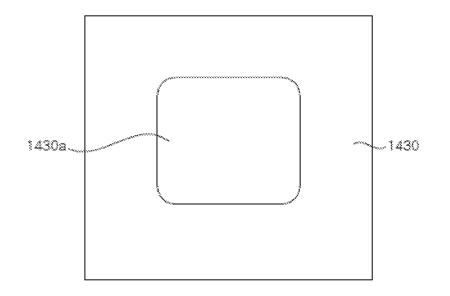

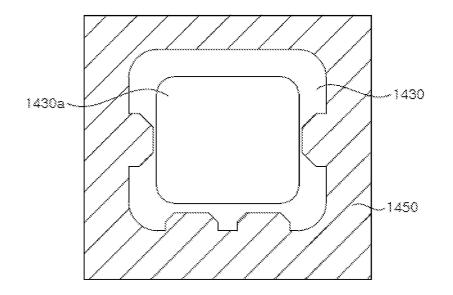

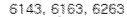

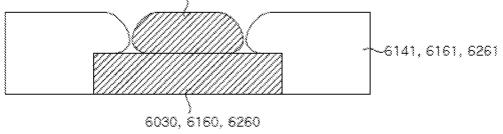

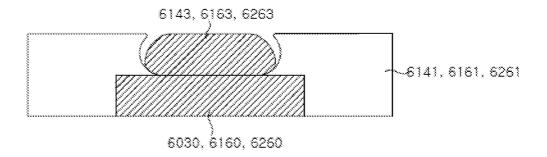

[0153] The first reflective electrode 25 is in ohmic contact with the p-type semiconductor layer of the first LED stack 23 and reflects the light generated from the first LED stack 23. For example, the first reflective electrode 25 may include an ohmic contact layer 25a and a reflective layer 25b.

[0154] The ohmic contact layer 25*a* is partially in contact with the p-type semiconductor layer. In order to prevent absorption of light by the ohmic contact layer 25a, the ohmic contact layer 25a may be formed in a predetermined area. For example, the ohmic contact layer 25*a* may be disposed near an edge of the first LED stack 23 and may be arranged substantially in an annular shape. A contact area of the ohmic contact layer 25a with respect to the first LED stack 23 may be 25% or less, or may be 10% or less in some exemplary embodiments. Even though the contact area of the ohmic contact layer 25a is relatively small, when an area of the first LED stack 23 is about 200 µm or less in size, a current may be evenly distributed in the first LED stack 23. The ohmic contact layer 25a may be formed of transparent conductive oxides or Au alloys, such as Au(Zn) or Au(Be). [0155] The reflective layer 25b may cover the ohmic contact layer 25a and the lower surface of the first LED stack 23. However, as shown in FIG. 1, the reflective layer 25b exposes the lower surface of the first LED stack 23 in regions around where the connectors 59a, 59b, 59c, and 59d are to be formed. More particularly, the reflective layer 25b may expose the lower surface of the first LED stack 23 in a region surrounded by the ohmic contact layer 25a. The reflective layer 25b may include a reflective metal layer formed of Al, Ag, or others. In addition, the reflective layer 25b may include a metal adhesion layer formed of Ti, Ta, Ni, Cr, or others on upper and lower surfaces of the reflective metal layer in order to improve adhesion of the reflective metal layer. The reflective layer 25b may be formed of a metal layer, which has a high reflectance to light generated from the first LED stack 23, for example, red light. Meanwhile, the reflective layer 25b may have a relatively low reflectance to light generated from the second LED stack 33 or the third LED stack 43, for example, green light or blue light. Therefore, the reflective layer 25b may reduce light interference by absorbing light generated from the second and third LED stacks 33 and 43 that is emitted toward the support substrate 51. Au has high reflectance to red light, and low reflectance to green light or blue light, and thus, may be used to form the reflective layer 25b disposed on the first LED stack 23.

**[0156]** The second transparent electrode **35** is in ohmic contact with the p-type semiconductor layer of the second LED stack **33**. The second transparent electrode **35** may be formed of a metal layer or conductive oxide layer transparent to red light and green light. The third transparent electrode **45** is in ohmic contact with the p-type semiconductor layer of the third LED stack **43**. The third transparent electrode **45** may be formed of a metal layer or conductive oxide layer transparent to red light, green light, and blue light. The second transparent electrode **35** and the third transparent electrode **45** may be in ohmic contact with the p-type semiconductor layer of each of the LED stacks to assist current distribution. Examples of the conductive oxide layer used for the second and third transparent electrodes **35** and **45** may include SnO<sub>2</sub>, InO<sub>2</sub>, ITO, ZnO, IZO or others.

[0157] The first color filter 37 may be disposed between the first LED stack 23 and the second LED stack 33. In addition, the second color filter 47 may be disposed between the second LED stack 33 and the third LED stack 43. The first color filter 37 may transmit light generated from the first LED stack 23 and reflects the light generated from the second LED stack 33. The second color filter 47 may transmit light generated from the first and second LED stacks 23 and 33 and reflect light generated from the third LED stack 43. As such, light generated from the first LED stack 23 may be emitted to the outside through the second LED stack 33 and the third LED stack 43, and light generated from the second LED stack 33 may be emitted to the outside through the third LED stack 43. Further, it may be possible to prevent light generated from the second LED stack 33 from being incident to the first LED stack 23 and being lost, or to prevent light generated from the third LED stack 43 from being incident to the second LED stack 33 and being lost.

**[0158]** In some exemplary embodiments, the first color filter **37** may also reflect light generated from the third LED stack **43**.

[0159] The first and second color filters 37 and 47 may be, for example, a low pass filter through which only a low wavelength region of light, e.g., light in a long wavelength region, a band pass filter through which only a certain wavelength region of light passes, or a band stop filter only blocking a certain wavelength region of light. More particularly, the first and second color filters 37 and 47 may be formed by alternately stacking insulating layers having different refractive indices. For example, the color filters may be formed by alternately stacking TiO<sub>2</sub> and SiO<sub>2</sub>. The first and second color filters 37 and 47 may include a distributed Bragg reflector (DBR). A stop band in the distributed Bragg reflector may be controlled by adjusting the thicknesses of TiO<sub>2</sub> and SiO<sub>2</sub>. The low pass filter and the band pass filter may also be formed by alternately stacking insulating layers having different refractive indices one above another.

**[0160]** The first bonding layer **55** couples the first LED stack **23** to the substrate **51**. As shown in the drawings, the first reflective electrode **25** may be in contact with the first bonding layer **55**. The first bonding layer **55** may be transmissive or non-transmissive.

[0161] The second bonding layer 65 couples the second LED stack 33 to the first LED stack 23. As shown in the drawings, the second bonding layer 65 may be in contact with the first LED stack 23 and the first color filter 37. The second bonding layer 65 transmits light generated from the first LED stack 23. The second bonding layer 65 may be formed of, for example, spin-on-glass having light transmitting property.

**[0162]** The third bonding layer **75** couples the third LED stack **43** to the second LED stack **33**. As shown in the drawings, the third bonding layer **75** may be in contact with the second LED stack **33** and the second color filter **47**. However, the inventive concepts are not limited thereto, and a transparent conductive layer may be disposed on the second LED stack **33**. The third bonding layer **75** transmits the light generated from the first LED stack **23** and the second LED stack **33**. The third bonding layer **75** may be formed of, for example, spin-on-glass having light transmitting property.

**[0163]** The bonding layers **55**, **65**, and **75** may be formed by forming transparent organic layers or transparent inorganic layer on each of the two objects to be bonded, and then bonding the objects with each other. Examples of an organic layer may include SU8, poly(methyl methacrylate) (PMMA), polyimide, parylene, benzocyclobutene (BCB), or others. Examples of an inorganic layer may include  $Al_2O_3$ , SiO<sub>2</sub>, SiNx, or others. The organic layers may be bonded at high vacuum and high pressure. Surfaces of the inorganic layers may be planarized by, for example, a chemical mechanical polishing (CMP), and then surface energy is lowered by plasma and the like, resulting in bonding at high vacuum.

[0164] A first-1 connector 59d electrically connects the first reflective electrode 25 and the electrode pad 53d to each other. As such, the first-1 connector 59d is electrically connected to the lower surface of the first LED stack 23. As shown in the drawings, the first-1 connector 59d may pass through the first LED stack 23. However, the inventive concepts are not limited thereto, and the first-1 connector 59d may be formed on a side surface of the first LED stack 23. The insulating layer 57 is interposed between the first-1 connector 59d and the first LED stack 23, thereby preventing the first-1 connector 59d from being short-circuited to the upper surface of the first LED stack 23.

[0165] A first-2 connector 59a electrically connects the upper surface of the first LED stack 23 and the electrode pad 53*a* on the substrate 51 to each other. The first-2 connector 59*a* may be connected to the upper surface of the first LED stack 23, and may pass through the first LED stack 23 to be connected to the electrode pad 53*a*. The insulating layer 57 may be interposed between the first LED stack 23 and the first-2 connector 59*a* from being short-circuited to the lower surface of the first LED stack 23.

[0166] A first-3 connector 59b and a first-4 connector 59c may pass through the first LED stack 23 to be connected to each of the electrode pads 53b and 53c. The first-3 connector 59b and the first-4 connector 59c are insulated from the first LED stack 23, by the insulating layer 57 interposed between the first LED stack 23 and the connectors 59b and 59c.

[0167] The first-3 connector 59b and the first-4 connector 59c may function as an intermediate connector, or these configurations may be omitted in some exemplary embodiments.

[0168] A second-1 connector 69d is disposed to electrically connect the second transparent electrode 35 to the electrode pad 53*d*. The second-1 connector 69d is electrically connected to the lower surface of the second LED stack 33 through the second transparent electrode 35. As shown in the drawings, the second-1 connector 69d may pass through the second LED stack 33. However, the inventive concepts are not limited thereto, and the second-1 connector 69d may be formed on a side surface of the second LED stack 33. The insulating layer 67 is interposed between the second-1 connector 69d and the second-1 connector 69d from being short-circuited to the upper surface of the second LED stack 33.

[0169] As shown in FIG. 2, the second-1 connector 69d may be connected to the first-1 connector 59d to be electrically connected to the electrode pad 53d. In this case, the first-1 connector 59d may function as an intermediate con-

nector. In addition, as shown in FIG. 2, the second-1 connector 69d may be stacked on the first-1 connector 59d in a vertical direction.

[0170] A second-2 connector 69b is disposed to electrically connect the upper surface of the second LED stack 33 to the electrode pad 53*b*. The second-2 connector 69b may be connected to the upper surface of the second LED stack 33, and may pass through the second LED stack 33. As shown in the drawings, the second-2 connector 69b may be connected to the first-3 connector 59b to be electrically connected to the electrode pad 53b. The second-2 connector 69b may be directly connected to the electrode pad 53b. In this case, the first-3 connector 59b is omitted.

[0171] The insulating layer 67 may be interposed between the second LED stack 33 and the second-2 connector 69*b* in order to prevent the second-2 connector 69*b* from being short-circuited to the lower surface of the second LED stack 33.

[0172] A second-3 connector 69c may be disposed to pass through the second LED stack 33. The second-3 connector 69c may be electrically connected to the electrode pad 53c, and may be connected to, for example, the first-4 connector 59c. The second-3 connector 69c is insulated from the second LED stack 33 by the insulating layer 67 interposed between the second LED stack 33 and the second-3 connector 69c.

[0173] The second-3 connector 69c may function as an intermediate connector, or these configurations may be omitted in some exemplary embodiments.

[0174] A third-1 connector 79d is disposed to connect the third transparent electrode 45 and the electrode pad 53d to each other. The third-1 connector 79d is electrically connected to the lower surface of the third LED stack 43 through the third transparent electrode 45. As shown in the drawings, the third-1 connector 79d may pass through the third LED stack 43. However, the inventive concepts are not limited thereto, and the third-1 connector 79d may be formed on a side surface of the third LED stack 43. The insulating layer 77 is interposed between the third-1 connector 79d and the third-1 connector 79d may preventing the third-1 connector 79d from being short-circuited to the upper surface of the third LED stack 43.

[0175] As shown in FIG. 2, the third-1 connector 79d may be connected to the second-1 connector 69d to be electrically connected to the electrode pad 53d. In this case, the second-1 connector 69d and the first-1 connector 59d may function as an intermediate connector. In addition, as shown in FIG. 2, the third-1 connector 79d may be stacked on the second-1 connector 69d in a vertical direction. Therefore, the first-1 connector 59d, the second-1 connector 69d, and the third-1 connector 79d are electrically connected to one another and are stacked in a vertical direction. The connectors are disposed in an emission direction of light to absorb light. In a case where the connectors are disposed to be spaced apart from one another in a lateral direction, a light emission area may be decreased and cause increased light loss. However, the connectors according to an exemplary embodiment are stacked in a vertical direction to reduce loss of light generated from the first LED stack 23 and the second LED stack 33 by the connectors.

[0176] A third-2 connector 79c is disposed to connect the upper surface of the third LED stack 43 and the electrode pad 53c to each other. The third-2 connector 79c may be connected to the upper surface of the third LED stack 43 and

may pass through the third LED stack **43**. As shown in the drawings, the third-2 connector **79**c may be connected to the second-3 connector **69**c to be electrically connected to the electrode pad **53**c. The third-2 connector **79**c may be directly connected to the electrode pad **53**c. In this case, the second-3 connector **69**c may be omitted.

[0177] Meanwhile, the insulating layer 77 may be interposed between the third LED stack 43 and the third-2 connector 79c in order to prevent the third-2 connector 79c from being short-circuited to the lower surface of the third LED stack 43.

[0178] As shown in the drawings, the third-2 connector 79c, the second-3 connector 69c, and the first-4 connector 59c may be stacked in a vertical direction, which may reduce loss of light.

**[0179]** To prevent light interference between the pixels due to light emission from the first LED stack 23, the second LED stack 33, and the third LED stack 43 to the side surfaces thereof, a light reflective layer or a light blocking material layer may be formed to cover side surfaces of the first to third LED stacks 23, 33, and 43. Examples of the light reflective layer may include a distributed Bragg reflector, or an insulating layer formed of SiO<sub>2</sub> with a reflective metal layer or a highly reflective organic layer deposited on the insulating layer. As the light blocking layer, for example, black epoxy may be used. The light blocking materials prevent light interference between light emitting elements to increase a contrast ratio of an image.

[0180] According to an exemplary embodiment, the first LED stack 23 is electrically connected to the electrode pads 53d and 53a, the second LED stack 33 is electrically connected to the electrode pads 53d and 53b, and the third LED stack 43 is electrically connected to the electrode pads 53d and 53c. As such, anodes of the first LED stack 23, the second LED stack 33, and the third LED stack 43 are commonly and electrically connected to the electrode pad 53d, and cathodes thereof are electrically connected to the electrode pads 53a, 53b, and 53c different from one another, respectively. Therefore, the first to third LED stacks 23, 33, and 43 may be independently driven. Further, these LED stacks 23, 33, and 43 may be disposed on the thin film transistor substrate 51 and may be electrically connected to the internal circuit of the substrate 51 to be driven in an active matrix manner.

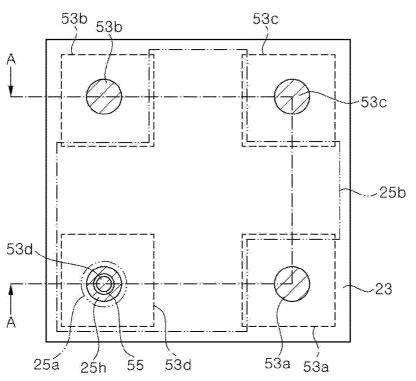

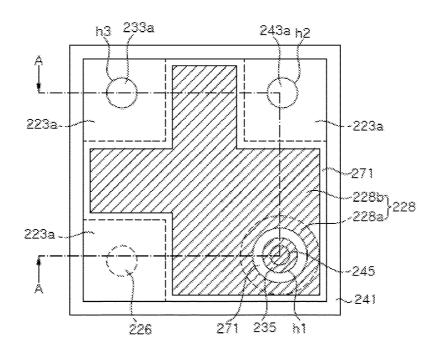

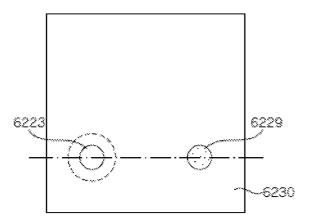

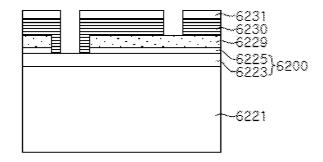

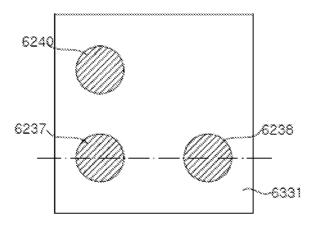

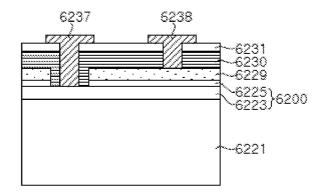

[0181] FIGS. 3A, 3B, 4A, 4B, 5A, 5B, 6A, 6B, 7A, 7B, 8A, 8B, 9A, 9B, 10A, 10B, 11A, 11B, 12A, 12B, 13A, 13B, 14A, 14B, 15A, 15B, 16A, and 16B are schematic plan views and schematic cross-sectional views illustrating a method of manufacturing a display apparatus according to an exemplary embodiment of the present disclosure. In the drawings, each plan view corresponds to the plan view of FIG. 1, and each cross-sectional view is taken along line A-A of FIG. 1.

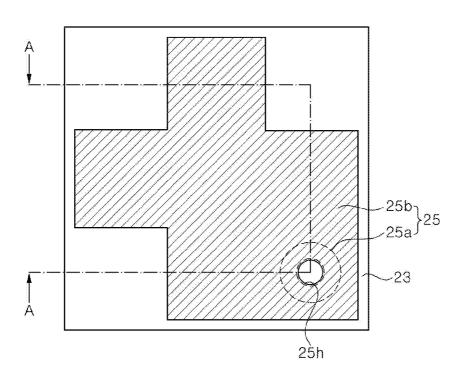

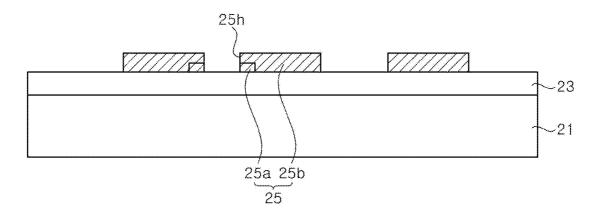

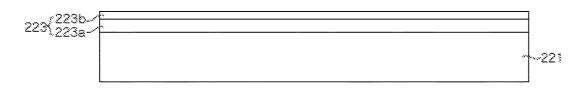

**[0182]** First, referring to FIGS. **3**A and **3**B, a first LED stack **23** is grown on a first substrate **21**. The first substrate **21** may be, for example, a GaAs substrate. In addition, the first LED stack **23** is formed of AlGaInP-based semiconductor layers, and includes an n-type semiconductor layer, an active layer, and a p-type semiconductor layer.

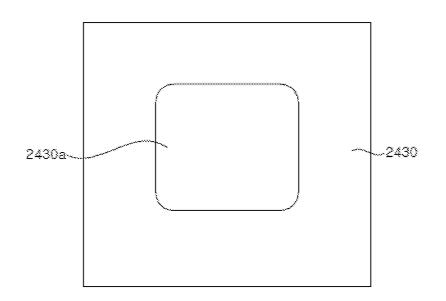

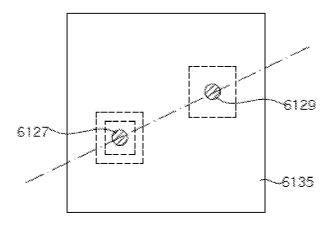

**[0183]** An ohmic contact layer 25a and a reflective layer 25b are formed on the first LED stack 23 to form a first reflective electrode 25. The ohmic contact layer 25a may be formed by using lift-off technique or the like, and may be formed to be disposed near an edge of the first LED stack 23.

As shown in the drawings, the ohmic contact layer **25***a* may be formed to have substantially an annular shape.

**[0184]** The reflective layer 25*b* covers the ohmic contact layer 25*a* and also covers the first LED stack 23. The reflective layer 25*b* may be formed to expose each of the edges of the first LED stack 23. More particularly, the reflective layer 25*b* may have an opening 25*h* exposing the first LED stack 23 with the ohmic contact layer 25*a*. The reflective layer 25*b* may be, for example, formed of Au and may be formed by using lift-off technique or the like.

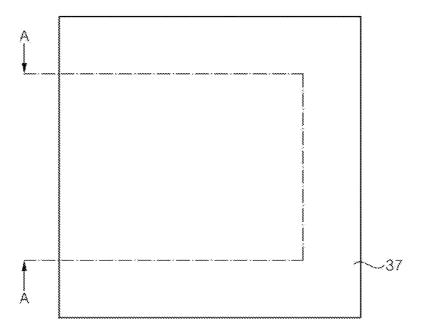

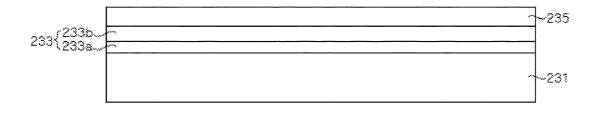

[0185] Referring to FIGS. 4A and 4B, a second LED stack 33 is grown on a second substrate 31, and a second transparent electrode 35 and a first color filter 37 are formed on the second LED stack 33. The second LED stack 33 may be formed of gallium nitride-based semiconductor layers and may include a GaInN-based well layer. The second substrate 31, on which gallium nitride-based semiconductor layers may be grown, is different from the first substrate 21. A composition ratio of GaInN may be determined such that the second LED stack 33 may emit green light. Meanwhile, the second transparent electrode 35 is in ohmic contact with a p-type semiconductor layer.

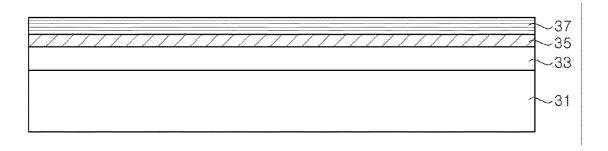

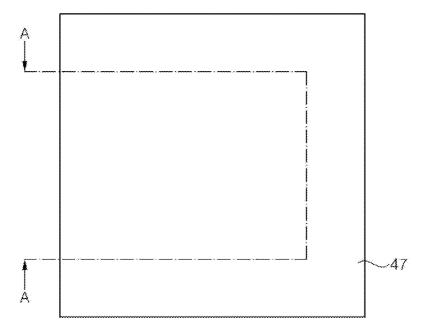

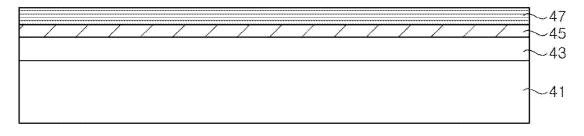

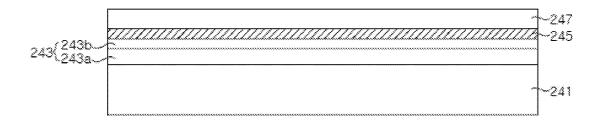

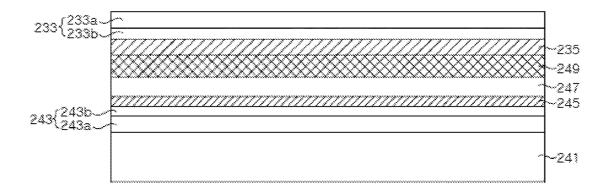

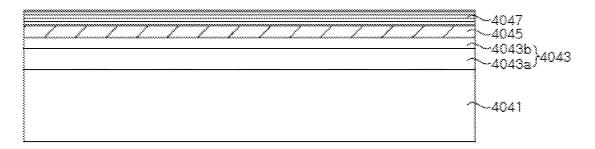

[0186] Referring to FIGS. 5A and 5B, a third LED stack 43 is grown on a third substrate 41, and a third transparent electrode 45 and a second color filter 47 are formed on the third LED stack 43. The third LED stack 43 may be formed of gallium nitride-based semiconductor layers and may include a GaInN-based well layer. The third substrate 41, on which gallium nitride-based semiconductor layers may be grown, is different from the first substrate 21. A composition ratio of GaInN may be determined such that the third LED stack 43 may emit blue light. Meanwhile, the third transparent electrode 45 is in ohmic contact with a p-type semiconductor layer.

**[0187]** The first color filter **37** and the second color filter **47** are substantially the same those as described with reference to FIG. **1**, therefore detailed descriptions thereof will be omitted to avoid redundancy.

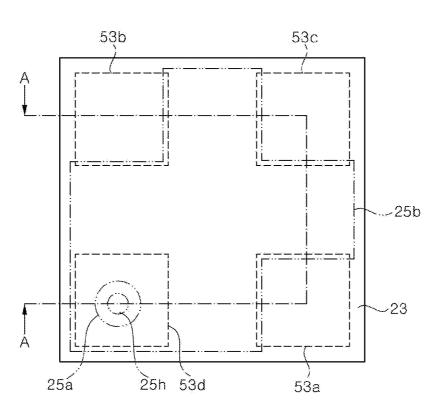

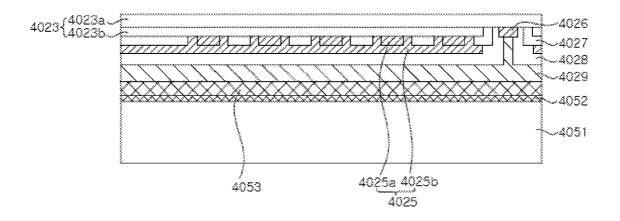

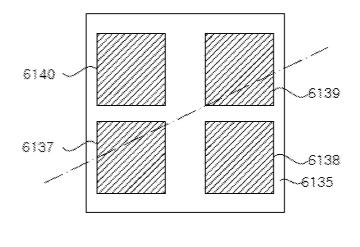

[0188] Referring to FIGS. 6A and 6B, electrode pads 53a, 53b, 53c, and 53d are formed on a substrate 51. The substrate 51 may be a substrate formed of Si, having thin film transistors therein. Each of the electrode pads 53a, 53b, 53c, and 53d corresponding to one pixel area may be disposed in each of the four edge regions of the substrate 51.

**[0189]** The first LED stack 23, the second LED stack 33, the third LED stack 43, and the electrode pads 53a, 53b, 53c, and 53d are separately formed on different substrates, and the forming sequence thereof is not particularly limited.

[0190] Referring to FIGS. 7A and 7B, the first LED stack 23 is coupled onto the substrate 51 via a first bonding layer 55. The first bonding layer 55 may be disposed on the substrate 51, and the first reflective electrode 25 is disposed to face the substrate 51 so that the first reflective electrode 25 is bonded to the first bonding layer 55. Alternatively, bonding material layers may be formed on each of the substrate 51 and the first LED stack 23, and then the first LED stack 23 may be coupled to the substrate 51 by bonding the bonding material layers each other. Meanwhile, the first substrate 21 may be removed from the first LED stack 23 by chemical etching, or the like. As such, the n-type semiconductor layer of the first LED stack 23 is exposed on the upper surface. The exposed n-type semiconductor layer may be subjected to surface texturing.

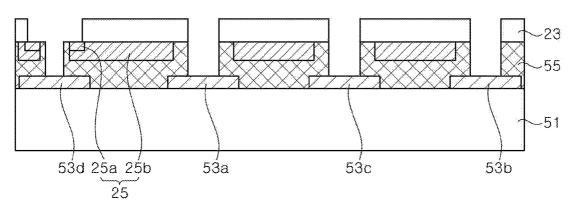

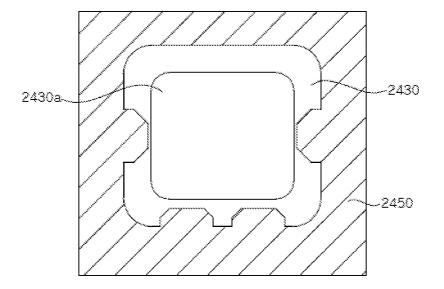

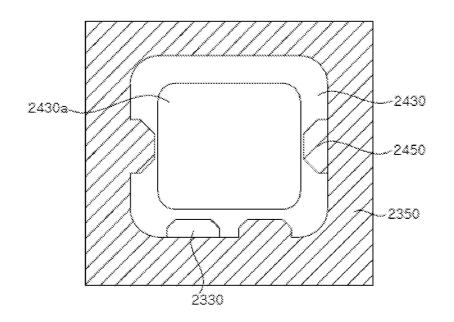

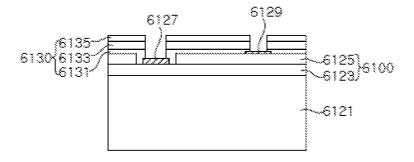

**[0191]** Referring to FIGS. **8**A and **8**B, the first LED stack **23** is patterned to expose a part of the first reflective electrode **25**. To avoid damages of the reflective layer **25***b*, the ohmic contact layer **25***a* may be exposed. In addition, the first LED stack **23** and the first bonding layer **55** are patterned to form openings for exposing the electrode pads **53***a*, **53***b*, **53***c*, and **53***d*.

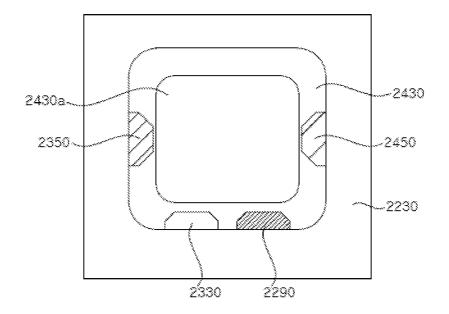

**[0192]** Referring FIGS. **9**A and **9**B, an insulating layer **57** is formed to cover side surfaces of the first LED stack **23** in the openings. The insulating layer **57** may also partially cover upper surfaces of the first LED stack **23**. The insulating layer **57** is formed to expose the first reflective electrode **25** and the electrode pads 53a, 53b, 53c, and 53d.

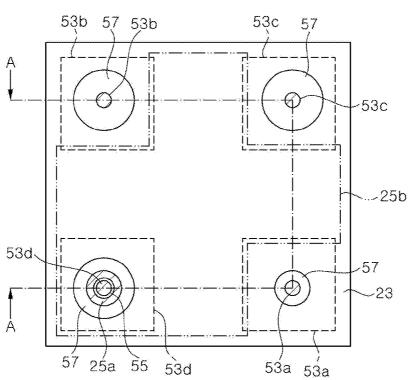

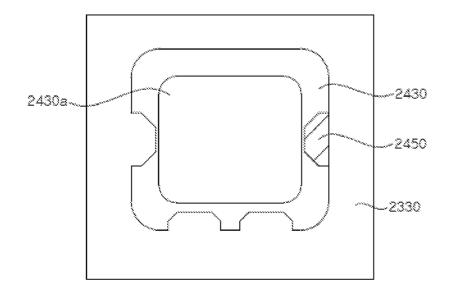

[0193] Referring FIGS. 10A and 10B, connectors 59a, 59b, 59c, and 59d are formed, which may be connected to the exposed electrode pads 53a, 53b, 53c, and 53d, respectively. A first-1 connector 59d is connected to the first reflective electrode 25 and also to the electrode pad 53d. Therefore, a lower surface of the first LED stack 23 and the electrode pad 53d are electrically connected to each other by the first-1 connector 59d. In addition, a first-2 connector 59a is connected to the electrode pad 53a. Therefore, the upper surface of the first LED stack 23 and also to the electrode pad 53a. Therefore, the upper surface of the first LED stack 23 and also to the electrode pad 53a. Therefore, the upper surface of the first-2 connector 59a. A first-3 connector 59b and a first-4 connector 59c are insulated from the first LED stack 23 by the insulating layer 57.

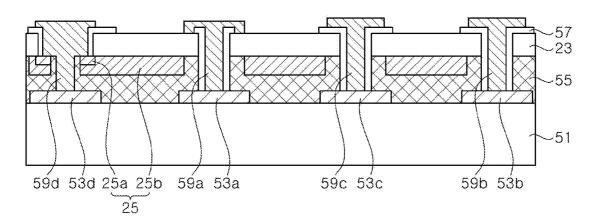

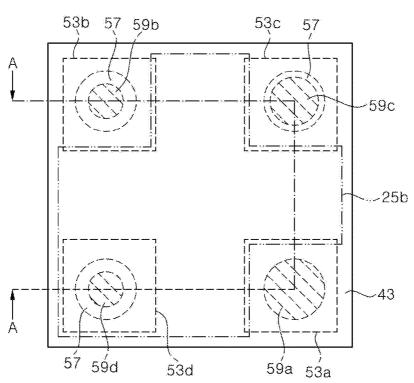

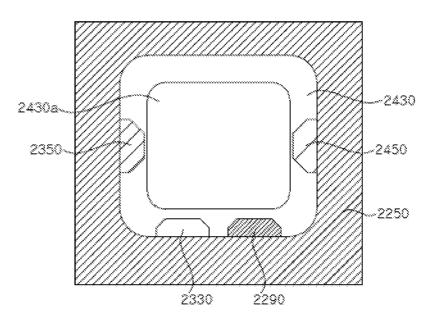

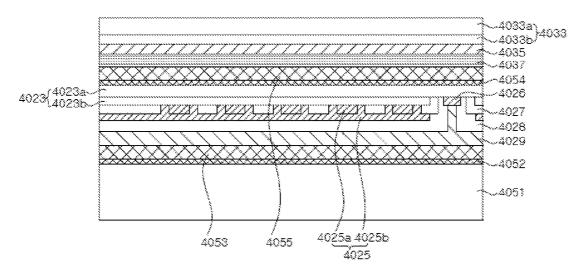

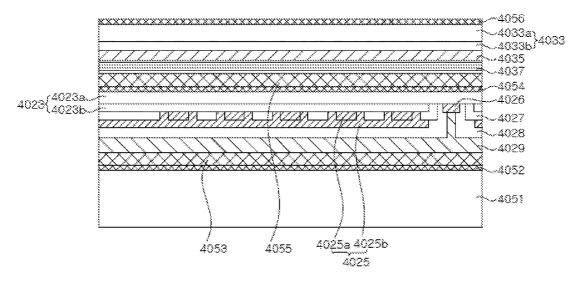

[0194] Referring to FIGS. 11A and 11B, the second LED stack 33 of FIGS. 4A and 4B is coupled onto the first LED stack 23, on which the first-1, first-2, first-3, and first-4 connectors 59d, 59a, 59b, and 59c are formed, via a second bonding layer 65. The first color filter 37 is bonded to the second bonding layer 65 and disposed to face the first LED stack 23. The second bonding layer 65 may be disposed on the first LED stack 23 in advance. The first color filter 37 may be bonded to the second bonding layer 65 and disposed to face the second bonding layer 65 and. Alternatively, the bonding material layers may be formed on each of the first LED stack 23 and the first color filter 37, and the bonding material layers are bonded to each other to couple the second LED stack 33 to the first LED stack 23. Meanwhile, the second substrate 31 may be separated from the second LED stack 33 by using laser lift-off, chemical lift-off techniques, or others. Therefore, the n-type semiconductor layer of the second LED stack 33 is exposed. The exposed n-type semiconductor layer may be subjected to surface texturing by chemical etching or the like. However, the step of surface texturing on the second LED stack 33 may be omitted in some exemplary embodiments.

[0195] Referring to FIGS. 12A and 12B, the second LED stack 33 is patterned to expose the second transparent electrode 35, and the exposed second transparent electrode 35, the first color filter 37, and the second bonding layer 65 are etched to form openings for exposing the first-1 connector 59*d*. In addition, the openings for exposing the first-3 connector 59*b* and the first-4 connector 59*c* may be formed together.

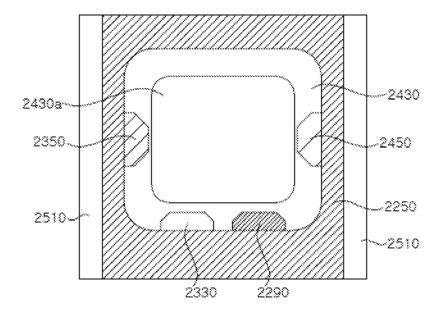

[0196] Referring FIGS. 13A and 13B, an insulating layer 67 covering sides of the exposed openings is formed. The insulating layer 67 exposes the second transparent electrode 35 and also exposes the first-1 connector 59*d*, the first-3 connector 59*b*, and the first-4 connector 59*c*.

[0197] A second-1 connector 69d, a second-2 connector 69b, and a second-3 connector 69c are formed in the openings. The second-1 connector 69d electrically connects the second transparent electrode 35 and the first-1 connector 59d to each other and is insulated from the upper surface of the second LED stack 33 by the insulating layer 67. The second-2 connector 69b is connected to the upper surface of the second LED stack 33 and to the first-3 connector 59b. The second-2 connector 69b is electrically connected to the electrode pad 53b through the first-3 connector 59b. The second-2 connector 69b is insulated from the lower surface of the second LED stack 33 and the second the second through the first-3 connector 59b. The second-2 connector 69b is insulated from the lower surface of the second LED stack 33 and the second transparent electrode 35 by the insulating layer 67.

[0198] Meanwhile, the second-3 connector 69c is connected to the first-4 connector 59c and is insulated from the second LED stack 33 and the second transparent electrode 35 by the insulating layer 67.